## THÈSE DE DOCTORAT

de l'Université de recherche Paris Sciences et Lettres PSL Research University

Préparée à l'École normale supérieure de Paris

Reverse Engineering Secure Systems Using Physical Attacks

École doctorale n°386 Sciences Mathématiques de Paris Centre

Spécialité Mathématiques

## Soutenue par Thibaut HECKMANN

le 18 Juin 2018, à l'École Militaire de Paris

Dirigée par Pr. David NACCACHE École normale supérieure

#### Composition du Jury

Pr. Konstantinos MARKANTONAKIS, Université de Londres, Royal Holloway, *Président du Jury*

Dr. Sergei SKOROBOGATOV, Université de Cambridge, Examinateur

Dr. Markus KUHN, Université de Cambridge, Examinateur

Pr. Ingrid VERBAUWHEDE, Université de Leuven, COSIC, Examinateur

Général d'armée Marc WATIN-AUGOUARD, Gendarmerie Nationale, Examinateur

Pr. Keith MAYES, Université de Londres, Royal Holloway, Rapporteur

Dr. Damien SAUVERON, XLIM, Université de Limoges, Rapporteur

Commandant/Dr. Thomas SOUVIGNET, Gendarmerie Nationale, Expert Invité

#### Thèse de Doctorat

# Rétro-Conception De Systèmes Sécurisés Par Attaques Physiques

Auteur: Thibaut HECKMANN

en vue de l'obtention du grade de

# Docteur de l'École normale supérieure de Paris spécialité Mathématiques

présentée et soutenue publiquement le 18 Juin 2018

devant le jury composé de:

Directeur de thèse: David Naccache (École normale supérieure de Paris)

Rapporteurs: Keith Mayes (Royal Holloway, Université de Londres)

Damien Sauveron (XLIM, Université de Limoges)

Examinateurs: Konstantinos Markantonakis (Royal Holloway, Université de Londres)

Sergei Skorobogatov (Université de Cambridge) Markus Kuhn (Université de Cambridge) Ingrid Verbauwhede (COSIC, Université de Leuven)

Marc Watin-Augouard (Gendarmerie Nationale)

Invité: Thomas Souvignet (Gendarmerie Nationale)

École doctorale 386: Sciences mathématiques de Paris Centre Unité de recherche: UMR 8548 - Département d'Informatique de l'École normale supérieure

#### Doctorate Dissertation

# Reverse Engineering Secure Systems Using Physical Attacks

Author: Thibaut HECKMANN

submitted in fulfillment of the requirements for the degree of

# Doctor of the École normale supérieure of Paris Mathematics Specialty

publicly defended and presented on June 18th, 2018

to the jury consisting of:

Supervisor: David Naccache (École normale supérieure of Paris)

Referees: Keith Mayes (Royal Holloway, University of London)

Damien Sauveron (XLIM, University of Limoges)

Examiners: Konstantinos Markantonakis (Royal Holloway, University of London)

Sergei Skorobogatov (University of Cambridge)

Markus Kuhn (University of Cambridge)

Ingrid Verbauwhede (COSIC, University of Leuven)

Marc Watin-Augouard (National Gendarmerie)

Guest member: Thomas Souvignet (National Gendarmerie)

Avec l'arrivée des dernières générations de téléphones chiffrés (BlackBerry PGP, iPhone), l'extraction des données par les experts est une tâche de plus en plus complexe et devient un véritable défi notamment après une catastrophe aérienne ou une attaque terroriste. Dans cette thèse, nous avons développé des attaques physiques sur systèmes cryptographiques à des fins d'expertises judiciaires.

Une nouvelle technique de re-brasage à basse température des composants électroniques endommagés, utilisant un mélange eutectique 42Sn/58Bi, a été développée. Nous avons exploité les propriétés physico-chimiques de colles polymères et les avons utilisées dans l'extraction de données chiffrées. Une nouvelle technique a été développée pour faciliter l'injection et la modification à haute-fréquence des données. Le prototype permet des analyses en temps réel des échanges processeur-mémoire en attaque par le milieu. Ces deux techniques sont maintenant utilisées dans des dispositifs d'attaques plus complexes de systèmes cryptographiques.

Nos travaux nous ont mené à sensibiliser les colles polymères aux attaques laser par pigmentation. Ce processus permet des réparations complexes avec une précision laser de l'ordre de 15 micromètres. Cette technique est utilisable en réparations judiciaires avancées des crypto-processeurs et des mémoires.

Ainsi, les techniques développées, mises bout à bout et couplées avec des dispositifs physiques (tomographie 3D aux rayons X, MEB, laser, acide fumant) ont permis de réussir des transplantations judiciaires de systèmes chiffrés en conditions dégradées et appliquées pour la première fois avec succès sur les téléphones BlackBerry chiffrés à l'aide de PGP.

**Mots Clés:** Retro-Conception Matérielle, Extractions Physiques, Attaques par le Milieu, Tomographie 3D aux Rayons X, Interactions Laser-Matière et Electron-Matière, Attaques Chimiques, Transplantations Judiciaires.

### Abstract

When considering the latest generation of encrypted mobile devices (BlackBerry's PGP, Apple's iPhone), data extraction by experts is an increasingly complex task. Forensic analyses even become a real challenge following an air crash or a terrorist attack. In this thesis, we have developed physical attacks on encrypted systems for the purpose of forensic analysis.

A new low-temperature re-soldering technique of damaged electronic components, using a 42Sn/58Bi eutectic mixture, has been developed. Then we have exploited the physico-chemical properties of polymer adhesives and have used them for the extraction of encrypted data. A new technique has been developed to facilitate injection and high-frequency data modification. By a man-in-the-middle attack, the prototype allows analysing, in real-time, the data exchanges between the processor and the memory. Both techniques are now used in more complex attacks of cryptographic systems.

Our research has led us to successfully sensitise polymer adhesives to laser attacks by pigmentation. This process allowed complex repairs with a laser with 15 micrometres precision and has been used in advanced forensic repair of crypto-processors and memory chips.

Finally, the techniques developed in this thesis, put end-to-end and coupled with physical devices (X-ray 3D tomography, laser, SEM, fuming acids), have made it possible to have successful forensic transplants of encrypted systems in degraded conditions. We have successfully applied them, for the first time, on a PGP-encrypted BlackBerry mobile phone.

**Keywords:** Hardware Reverse Engineering, Physical Extractions, Man-In-The-Middle Attacks, X-ray 3D Tomography, Laser-Matter and Electron-Matter Interactions, Chemical Attacks, Forensic Transplantations.

# Acknowledgements

This thesis is the outcome of three years of work in the Computer Science Department's Information Security Group of the École normale supérieure (ENS) of Paris. This work would not have been possible without the support of many people that I would like to thank here.

First of all, I would like to express my gratitude to Prof. David Naccache, my thesis advisor, for his unfailing support. He had believed very early in the potential of our research. An altruistic scientist, a member of the Institut Universitaire of France, ENS's ISG director and forensic expert for the International Criminal Court of The Hague: I wish to express the honour and the unbounded privilege which have been mine to be able to conduct my research by his side.

I wish to thank Major Thomas Souvignet for introducing me to this thesis work, for his involvement in our publications and the attentive technical proofreading of this manuscript. I owe him a lot for all he has done for me.

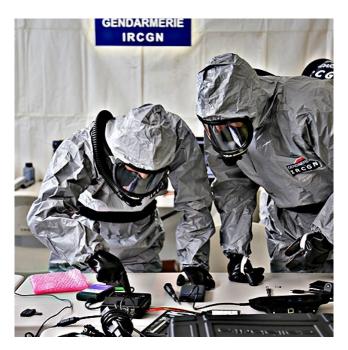

I express my deepest respect to all my Gendarmerie commanders for having believed in me. I hugely thank General Daoust who managed to convince the Gendarmerie's highest echelons before the CEST commission. I thank my direct chain of command, General Touron, Director of the Forensic Sciences Institute of the French Gendarmerie (IRCGN), as well as my Divisional Director, Colonel Strebel, Major Rubens and Major Letrillard. I will never forget their contributions as I now understand that officers' decisions are required to support the projects we believe in.

I would like to widely thank my proofreader, Dame Natacha Laniado, English Lecturer at Panthéon Assas University and PhD pastoral care at ENS Paris, who has helped me to proofread and correct this thesis and our papers.

I would also like to thank the entire Royal Holloway, University of London (RHUL) Computer Science Department, the Information Security Group team and the Smart Card and IoT Security Centre Laboratory, that helped me throughout my thesis, and especially Prof. Keith Mayes, Head of School of Mathematics and Information Scurity Group (ISG), Prof. Konstantinos Markantonakis, Director of the ISG Smart Card and IoT Security Centre and Dr Akram Raja Naeem for their advice, thesis proofreading and precious help. I thank you for your good humour and high level of competence that you shared. I thank all the RHUL's Chemistry Department and School of Biological Sciences, especially Prof. James McEvoy for his help during chemical attacks on electronic components.

I would warmly like to thank the University of Cambridge Computer Laboratory, especially Dr Sergei Skorobogatov and Dr Markus Kuhn from the Tamper And Monitoring Protection Engineering Research (TAMPER), for all close technical exchanges, information sharing, and to have accepted to be members of my thesis jury.

I would like to thank Dr Damien Sauveron from XLIM, University of Limoges, for the careful technical review of this manuscript.

I thank Graham Houghton, volunteer at Strode's College, who has helped me to proofread and correct this thesis. He very generously offered me help that proved to be valuable for finalising the thesis.

I am grateful to everyone who has worked with me on various topics, and especially my team at the IRCGN, officers and NCOs. The diversity of their profiles and competences undeniably constitute the strength of this fantastic unit.

I would like to express my recognition to the referees and examiners for their interest in my work, for agreeing to be part of my thesis jury and for providing me with their support and advice.

On a more personal note, I wish to thank my close family who believed in me, especially my wife, my parents and my brother. Without them none of this would have been possible —my wife, my pride; my parents, eternal support; and my brother, my role model. A special thank you to those who are no longer here, especially my grandparents, who have made me who I am today.

London, UK, March 12th, 2018, Thibaut HECKMANN

| "Above all, do not tell me it is impossible." General Philippe LECLER | RC                 |

|-----------------------------------------------------------------------|--------------------|

|                                                                       |                    |

|                                                                       |                    |

|                                                                       |                    |

| To my wife, to my parents, to my broth                                | her, to my family. |

|                                                                       |                    |

# Contents

|                 | Res             | ume               |                                                                                | i    |  |  |  |  |

|-----------------|-----------------|-------------------|--------------------------------------------------------------------------------|------|--|--|--|--|

|                 | Abs             | stract            |                                                                                | ii   |  |  |  |  |

|                 | Acknowledgments |                   |                                                                                |      |  |  |  |  |

|                 | Contents        |                   |                                                                                |      |  |  |  |  |

| List of Figures |                 |                   |                                                                                |      |  |  |  |  |

|                 | List            | of Ta             | bles                                                                           | xvii |  |  |  |  |

| 1               | Intr            | $\mathbf{coduct}$ | ion                                                                            | 1    |  |  |  |  |

|                 | 1.1             | Forens            | sic Investigators in the Face of Cryptography: French Law                      | 3    |  |  |  |  |

|                 |                 | 1.1.1             | The Birth of Cryptography in French Law                                        | 3    |  |  |  |  |

|                 |                 | 1.1.2             | The Criminal Sanctions Against the Illegal Use of Cryptography .               | 5    |  |  |  |  |

|                 |                 | 1.1.3             | Extracting Encrypted Data: the Experts' Work Legitimacy                        | 6    |  |  |  |  |

|                 | 1.2             | Thesis            | S Outline                                                                      | 7    |  |  |  |  |

|                 | 1.3             | Public            | eations                                                                        | 9    |  |  |  |  |

| <b>2</b>        | The             | eory              |                                                                                | 14   |  |  |  |  |

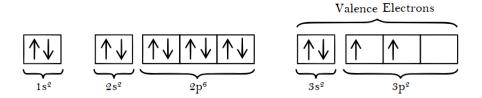

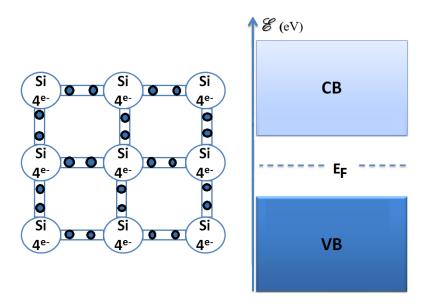

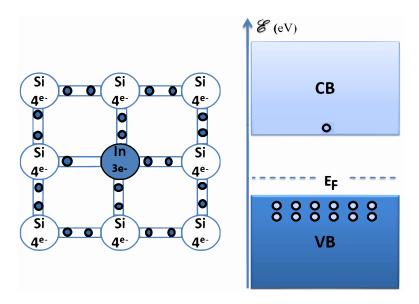

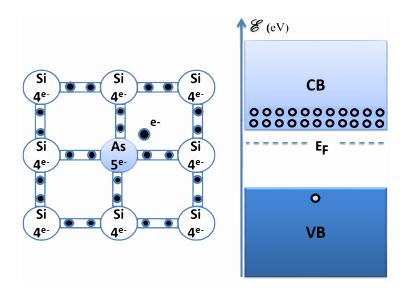

|                 | 2.1             | Gener             | al Semiconductor Theory and Fundamental Operations                             | 14   |  |  |  |  |

|                 |                 | 2.1.1             | Semiconductor Technology: Silicon                                              | 14   |  |  |  |  |

|                 |                 |                   | 2.1.1.1 Silicon Without an Electric Field $\overrightarrow{E}$ : Thermodynamic |      |  |  |  |  |

|                 |                 |                   | Equilibrium                                                                    | 19   |  |  |  |  |

|                 |                 |                   | 2.1.1.2 Silicon in an Electric Field $\overrightarrow{E}$ : Out Of Equilibrium | 22   |  |  |  |  |

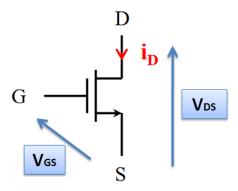

|                 |                 | 2.1.2             | Transistor Technologies                                                        | 24   |  |  |  |  |

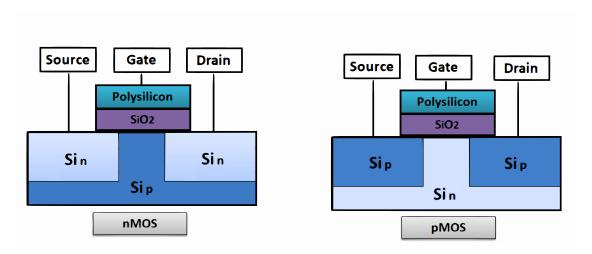

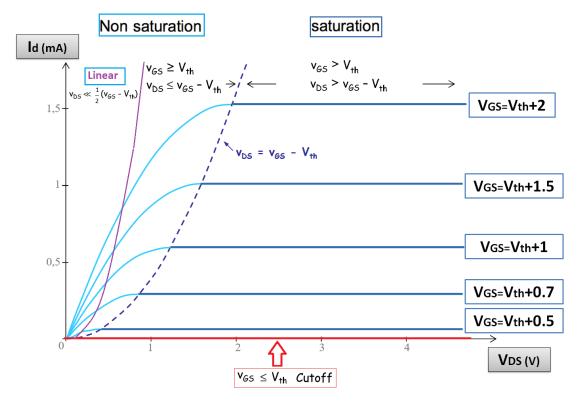

|                 |                 |                   | 2.1.2.1 The CMOS Transistor                                                    | 24   |  |  |  |  |

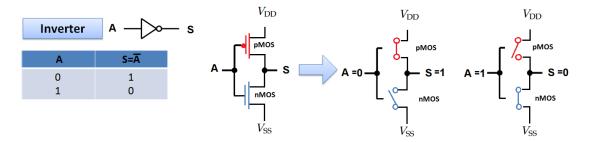

|                 |                 |                   | 2.1.2.2 The Inverter in CMOS Technology                                        | 27   |  |  |  |  |

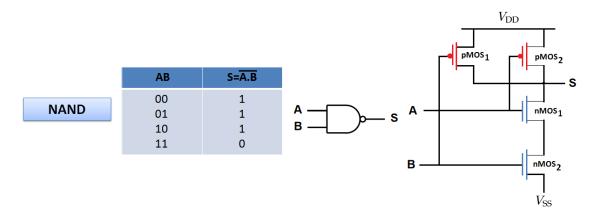

|                 |                 |                   | 2.1.2.3 The NAND Gate in CMOS Technology                                       | 28   |  |  |  |  |

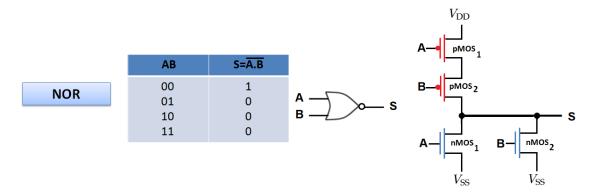

|                 |                 |                   | 2.1.2.4 The NOR Gate in CMOS Technology                                        | 30   |  |  |  |  |

|                 |                 |                   | 2.1.2.5 Complex Electronic Circuits                                            | 30   |  |  |  |  |

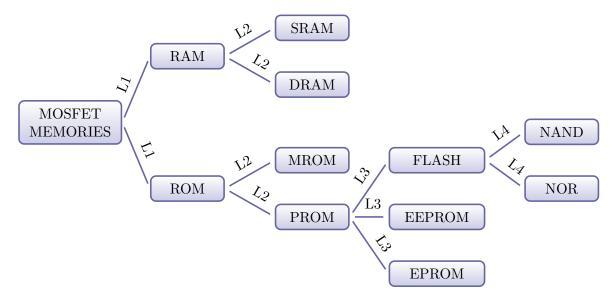

|                 | 2.2             | The V             | Tarious Types of Silicon Memories                                              | 31   |  |  |  |  |

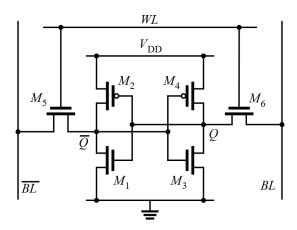

|                 |                 | 2.2.1             | Volatile Memories                                                              | 32   |  |  |  |  |

|                 |                 | 2.2.2             | Non-Volatile Memories                                                          | 33   |  |  |  |  |

|                 | 2.3             | Chip I            | Memory Manufacturing Process                                                   | 37   |  |  |  |  |

| 3               | For             | ensic I           | nvestigators Facing Data Recovery From Mobile Phones                           | 42   |  |  |  |  |

|                 | 3.1             | Tradit            | ional Forensic Techniques Used to Extract Data from Undamaged                  |      |  |  |  |  |

|                 |                 | Mobile            | a Devices                                                                      | 49   |  |  |  |  |

|   |     | 3.1.1    | Manual     | Extraction                                               | 43 |

|---|-----|----------|------------|----------------------------------------------------------|----|

|   |     | 3.1.2    | Logical 1  | Extraction                                               | 45 |

|   | 3.2 | Physic   | al Extrac  | tion                                                     | 46 |

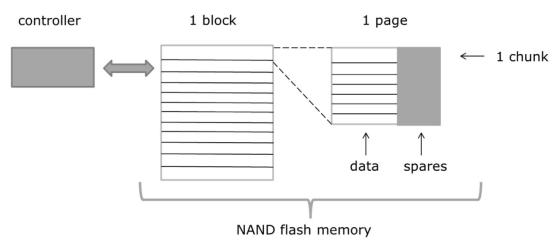

|   |     | 3.2.1    | Flash M    | emory Management Mechanisms                              | 48 |

|   |     | 3.2.2    | Physical   | Extraction Using Flasher-Boxes/Boot-Loader/JTAG          | 52 |

|   |     |          | 3.2.2.1    | Physical Extraction Using Mobile Phone Flasher Boxes .   | 52 |

|   |     |          | 3.2.2.2    | Physical Extraction Using a Boot Loader                  | 53 |

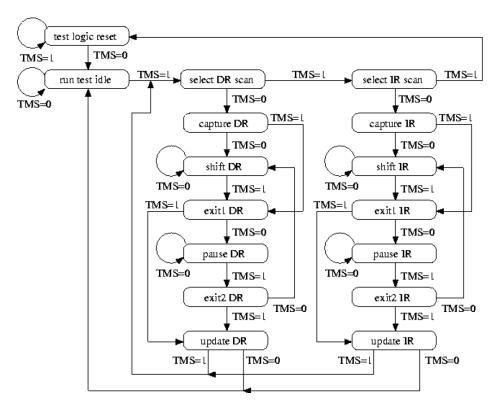

|   |     |          | 3.2.2.3    | Physical Extraction Using Joint Test Action Group (JTAG) | 54 |

|   |     | 3.2.3    | Physical   | Extraction Using Chip-off Methods: Unsoldering/Lapping   |    |

|   |     |          | and Mer    | nory Reading                                             | 55 |

|   |     |          | 3.2.3.1    | Unsoldering Technique                                    | 55 |

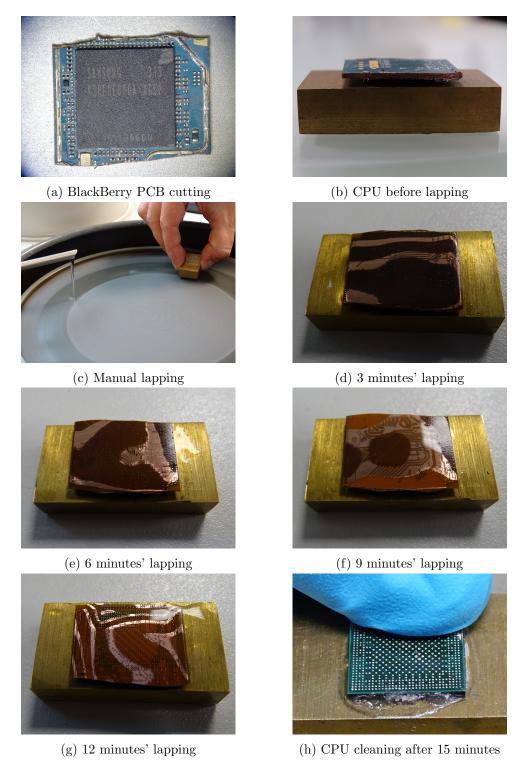

|   |     |          | 3.2.3.2    | Lapping Technique                                        | 57 |

|   |     |          | 3.2.3.3    | Memory Reader                                            | 59 |

|   |     | 3.2.4    | Physical   | Extraction Using Chip-On: Acid/Laser Attack and Mem-     |    |

|   |     |          | ory Read   | ling by Micro-Probing                                    | 62 |

|   |     |          | 3.2.4.1    | Chip-On Method: Acid Attack and Memory Reading by        |    |

|   |     |          |            | Micro-Probing                                            | 62 |

|   |     |          | 3.2.4.2    | Chip-On Method: Ablation Laser and Memory Reading        |    |

|   |     |          |            | by Micro-Probing                                         | 64 |

|   |     | 3.2.5    | Physical   | Extraction Using Micro-Read                              | 70 |

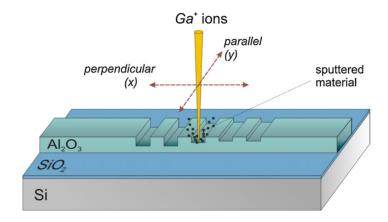

|   |     |          | 3.2.5.1    | Sample Preparation by Focused Ion Beam                   | 70 |

|   |     |          | 3.2.5.2    | Sample Preparation by Micro-Lapping and Reverse En-      |    |

|   |     |          |            | gineering                                                | 71 |

|   |     |          | 3.2.5.3    | Sample Preparation by Acid Attack                        | 72 |

|   |     |          | 3.2.5.4    | Micro-Read Process                                       | 72 |

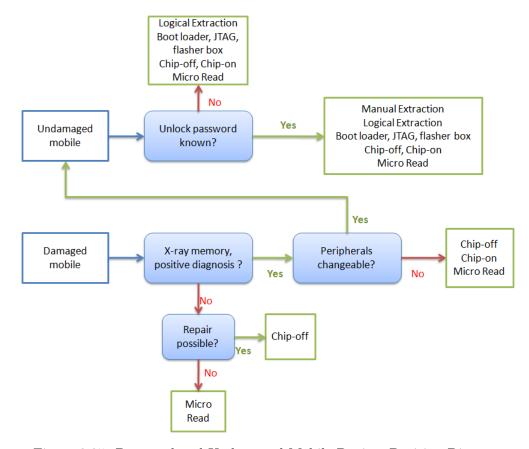

|   | 3.3 | Tradit   | ional Fore | ensic Techniques Used to Extract Data from Damaged Mo-   |    |

|   |     |          |            |                                                          | 73 |

|   | 3.4 | Transp   | olantation | : Advanced Forensic Techniques Used to Extract Data      |    |

|   |     | from I   | Damaged    | and Secured Mobile Devices                               | 76 |

| 4 | Chi | n-off Iı | mnroven    | nent: the Role of 42Sn/58Bi Solder                       | 79 |

| • | 4.1 | _        | -          | ot Stress Components During Investigations               | 79 |

|   | 4.2 |          |            | · · · · · · · · · · · · · · · · · · ·                    | 80 |

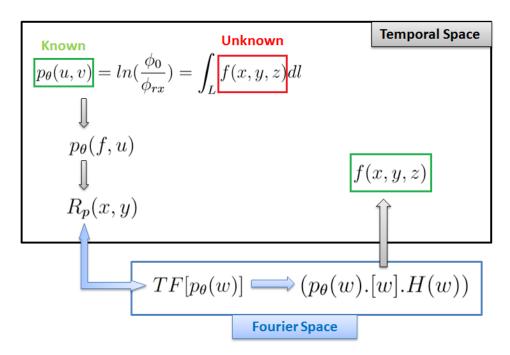

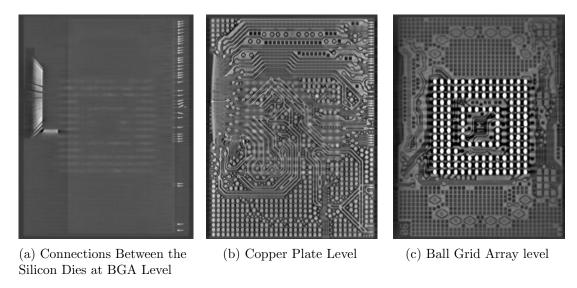

|   | 1.2 | 4.2.1    |            | omography                                                | 80 |

|   |     | 1.2.1    | 4.2.1.1    | Acquisition                                              | 81 |

|   |     |          | 4.2.1.2    | Reconstruction                                           | 83 |

|   |     |          | 4.2.1.3    | Post Treatment                                           | 86 |

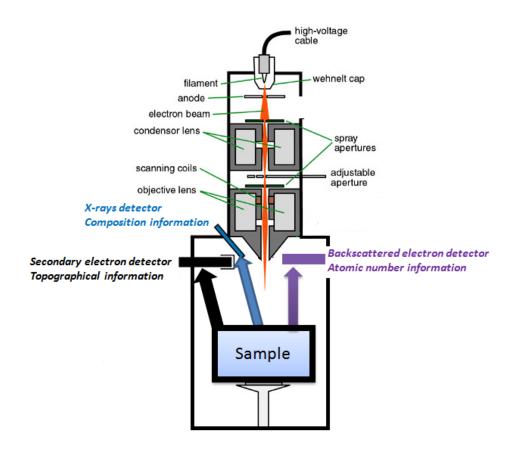

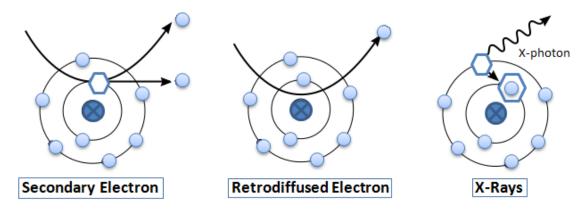

|   |     | 4.2.2    |            | g Electron Microscopy (SEM)                              | 86 |

|   |     | 4.2.3    |            | Bi Fundamental Properties                                | 89 |

|   | 4.3 |          | •          | ped                                                      | 92 |

|   |     |          | . 1        | •                                                        |    |

|   | 4.4            | ъ.            | L LD L                                                        | 0.0 |

|---|----------------|---------------|---------------------------------------------------------------|-----|

|   | 4.4            | •             | imental Results                                               |     |

|   |                | 4.4.1         | Main Results                                                  |     |

|   |                | 4.4.2         | Stencil Selection                                             |     |

|   |                | 4.4.3         | Reflow Error Analysis                                         |     |

|   |                | 4.4.4         | Conclusion of the Experiments                                 | 102 |

| 5 | $\mathbf{Adl}$ | nesives       | in Advanced Forensics Data Extraction                         | 104 |

|   | 5.1            | Conte         | xt                                                            | 104 |

|   | 5.2            | Materi        | ial                                                           | 104 |

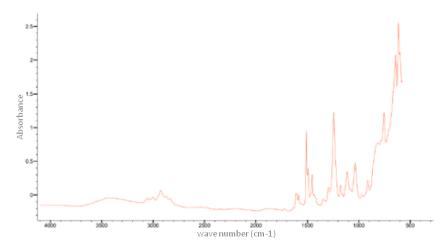

|   |                | 5.2.1         | Thermally Conductive Adhesives                                | 104 |

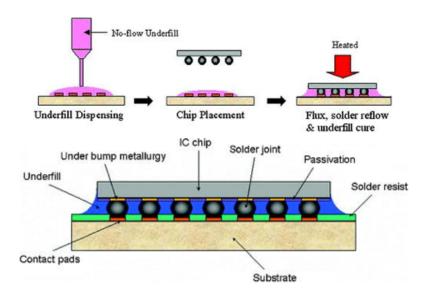

|   |                | 5.2.2         | Underfill: A Special Type of Thermally Conductive Adhesive    | 106 |

|   |                |               | 5.2.2.1 What is an Underfill Epoxy?                           | 106 |

|   |                |               | 5.2.2.2 Underfill Problem for Forensic Investigations         | 109 |

|   |                | 5.2.3         | UV-Curable Adhesives                                          | 110 |

|   |                | 5.2.4         | Electrically Conductive Adhesives                             | 111 |

|   | 5.3            | Digita        | l Forensic Applications and Developed Methods                 | 112 |

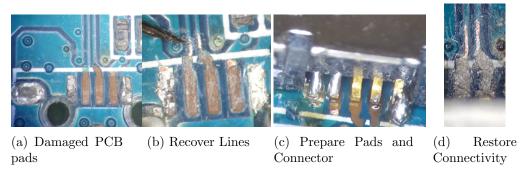

|   |                | 5.3.1         | Restoring Conductivity                                        | 112 |

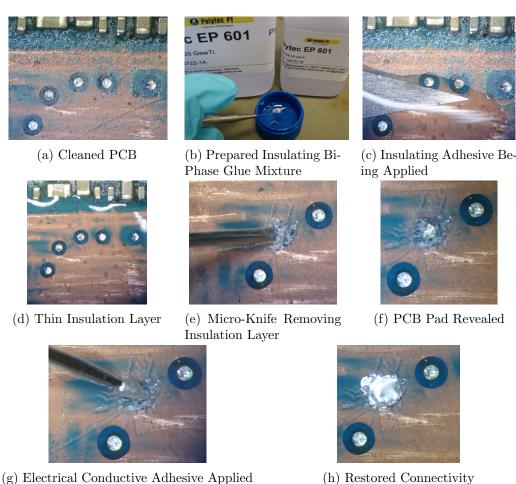

|   |                | 5.3.2         | Restoring Insulation                                          | 113 |

|   |                | 5.3.3         | Reworking and Prototyping                                     | 114 |

|   | 5.4            | Memo          | ry Man-In-The-Middle Attack                                   | 115 |

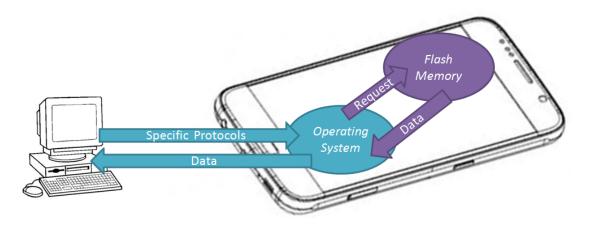

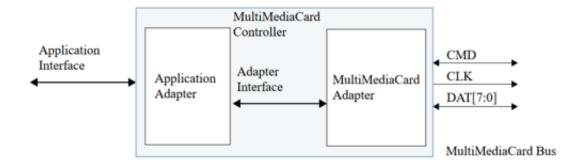

|   |                | 5.4.1         | eMMC: Embedded Multimedia Card                                | 115 |

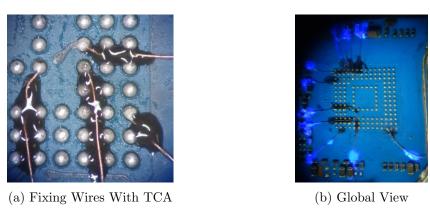

|   |                | 5.4.2         | Steps of the Prototype                                        | 119 |

|   |                | 5.4.3         | Reading Phase in Forensic Conditions                          | 123 |

|   |                | 5.4.4         | Injection Phase                                               | 123 |

|   |                | 5.4.5         | Tracking Signals Using a Logic Analyser or an FPGA            | 124 |

|   |                | 5.4.6         | Conclusion of the Experiments                                 | 125 |

| 6 | Las            | er Atta       | acks on Pigmented Electrically Conductive Adhesive (ECA)      | 127 |

| Ū | 6.1            |               | xt                                                            |     |

|   | 6.2            |               | se of the Developed Technique                                 |     |

|   |                | 6.2.1         | Materials                                                     |     |

|   |                |               | 6.2.1.1 Electrically Conductive Adhesives: EC151L             |     |

|   |                |               | 6.2.1.2 Laser IC Decapsulation                                |     |

|   |                | 6.2.2         | Theoretical Method                                            |     |

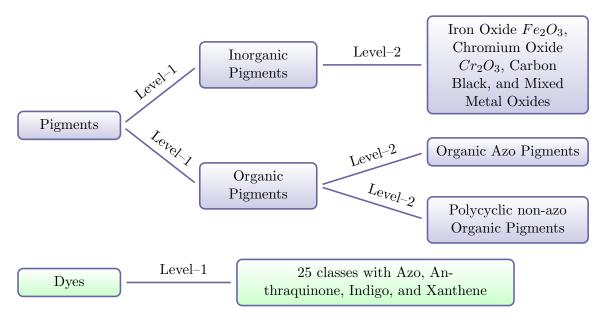

|   |                |               | 6.2.2.1 Theoretical Study of Main Pigments and Dyes           |     |

|   |                |               | 6.2.2.2 Choice of Our Dye and Pigments                        |     |

|   | 6.3            | Experi        | imental Results                                               |     |

|   | 2.0            | 6.3.1         | Experimental Method                                           |     |

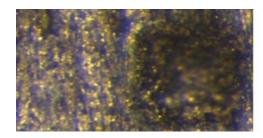

|   |                | 6.3.2         | Interaction Results (1064 nm Laser–EC151L) Without Dye and    | 100 |

|   |                | 5.5. <b>2</b> | Pigment                                                       | 134 |

|   |                | 6.3.3         | Interaction Results (1064 nm Laser–EC151L) With Indigotin Dye | 135 |

|   |                |               | ,                                                             |     |

|              |      | 6.3.4   | Interaction Results (1064 nm Laser–EC151L) With Eriochrome                    |     |

|--------------|------|---------|-------------------------------------------------------------------------------|-----|

|              |      |         | Black T Pigment                                                               | 136 |

|              |      | 6.3.5   | Interaction Results (1064 nm Laser–EC151L) With Sudan Black                   |     |

|              |      |         | Pigment                                                                       | 137 |

|              | 6.4  | Direct  | For<br>ensic Application: Repair of a Broken Bonding Wire $\ \ldots \ \ldots$ | 138 |

|              | 6.5  | Discus  | sion of the Experimental Results                                              | 141 |

|              |      | 6.5.1   | Limit of the Amount of Dye and Pigment on the Structure of the                |     |

|              |      |         | Adhesive                                                                      | 141 |

|              |      | 6.5.2   | How to Choose Between Pigment and Dye?                                        | 141 |

|              | 6.6  | Conclu  | usion of the Experiments                                                      | 142 |

| 7            | Adv  | vanced  | Transplantation Technique                                                     | 143 |

|              | 7.1  | Backgr  | round and Limits                                                              | 143 |

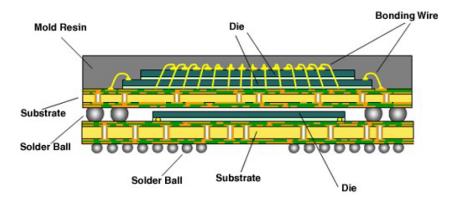

|              |      | 7.1.1   | What is a PoP Component?                                                      | 143 |

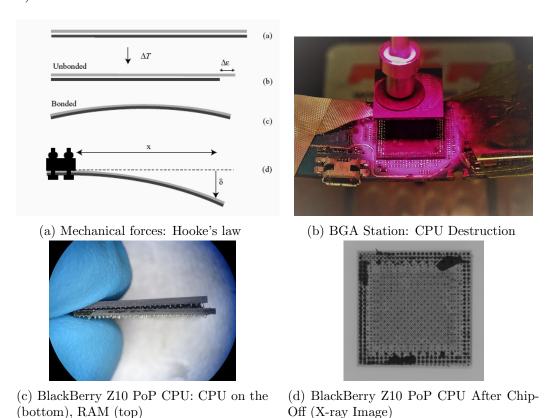

|              |      | 7.1.2   | Traditional Techniques and Their Limits                                       | 145 |

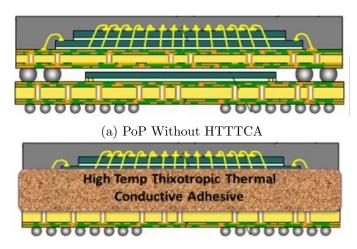

|              | 7.2  | PoP C   | Chip-off/TCA Adhesive Method                                                  | 146 |

|              |      | 7.2.1   | High Temp Thixotropic Thermal Conductive Adhesive (HTTTCA)                    | 146 |

|              | 7.3  | Metho   | d                                                                             | 146 |

|              |      | 7.3.1   | Applied Method                                                                | 146 |

|              | 7.4  | BlackF  | Berry 9900 PGP Transplantation                                                | 151 |

|              |      | 7.4.1   | BlackBerry PGP Cryptography Process                                           | 151 |

|              |      | 7.4.2   | BlackBerry 9900 PGP Physical Transplantation                                  | 152 |

|              | 7.5  | Discus  | sion                                                                          | 157 |

|              |      | 7.5.1   | Choice of Adhesives and Limits                                                | 157 |

|              |      | 7.5.2   | Which Electronic Components Should Be Transplanted?                           | 157 |

|              |      | 7.5.3   | Transplantation's Limit                                                       | 158 |

|              | 7.6  | Conclu  | usion of the Experiments                                                      | 158 |

| 8            | Con  | clusio  | n                                                                             | 159 |

|              | Bib  | liograp | bhy                                                                           | 165 |

| Aj           | ppen | dices   |                                                                               | 175 |

| $\mathbf{A}$ | Cal  | culatin | g Methods: Silicon Energy Bands' Structure                                    | 176 |

|              | A.1  | Schröd  | linger Equation                                                               | 176 |

|              | A.2  | Born-   | Oppenheimer and Adiabatic Approximations                                      | 177 |

|              | A.3  | Hartre  | ee–Fock Approximation                                                         | 177 |

| В            | Mai  | in Fore | ensic File Signatures Table                                                   | 179 |

# List of Figures

| 1.1  | The Broad Fields of Cryptography [Menezes et al., 1997]                 |

|------|-------------------------------------------------------------------------|

| 2.1  | Silicon Electron Configuration                                          |

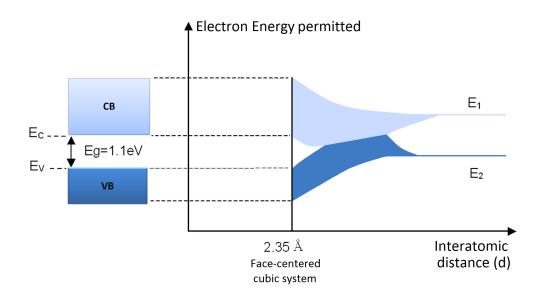

| 2.2  | Si Atoms in Crystalline Meshes: Valence Electrons' Energy Bands 18      |

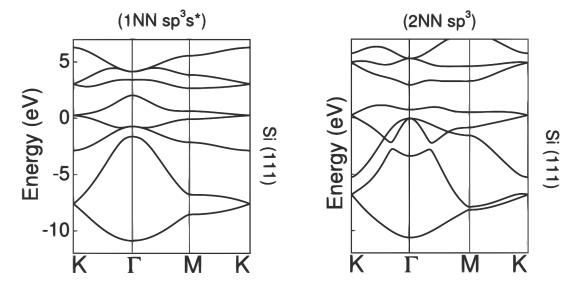

| 2.3  | Band Structure of Si(111) Obtained from TB Models: First-Nearest Neigh- |

|      | bour (1NN) sp3s* (Left), First-Nearest Neighbour (2NN) sp3 (Right) 16   |

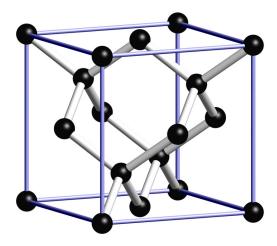

| 2.4  | Silicon is Crystallised in a Diamond Structure                          |

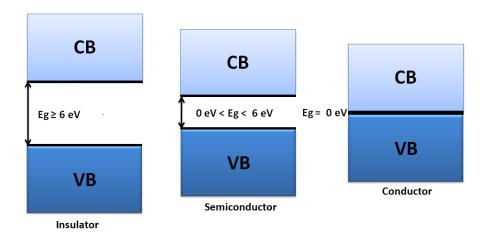

| 2.5  | Insulator, Semiconductor and Conductor Gap Energies                     |

| 2.6  | Intrinsic Silicon at $T = 0 K \dots 20$                                 |

| 2.7  | P-Type Silicon Crystal Doped With Indium Impurities                     |

| 2.8  | N-Type Silicon Crystal Doped With Arsenic Impurities                    |

| 2.9  | CMOS Switch                                                             |

| 2.10 | nMOS (Left) and pMOS (Right)                                            |

| 2.11 | Circuit nMOS: $I = f(V)$                                                |

| 2.12 | Inverter in CMOS Technology                                             |

| 2.13 | NAND Gate in CMOS Technology                                            |

| 2.14 | NOR Gate in CMOS Technology                                             |

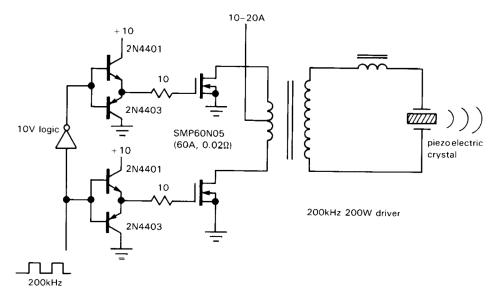

| 2.15 | Bipolar Power Piezo Driver [Horowitz and Hill, 1989]                    |

| 2.16 | MOS-Memories Tree                                                       |

| 2.17 | SRAM Logic Cell                                                         |

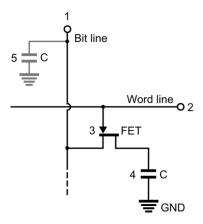

| 2.18 | DRAM Logic Cell                                                         |

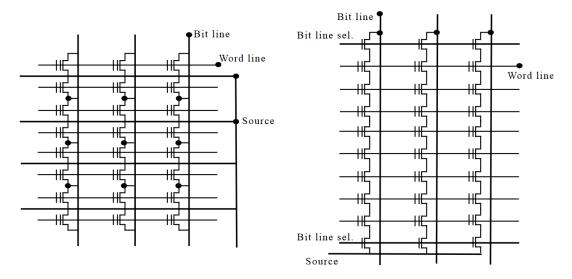

| 2.19 | NOR and NAND [Campardo et al., 2010]                                    |

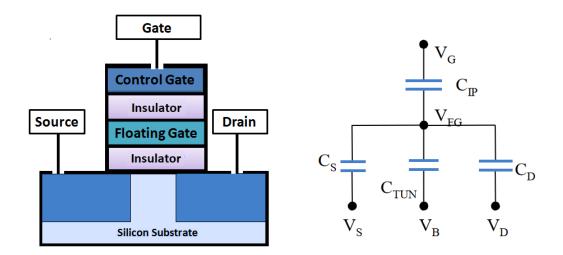

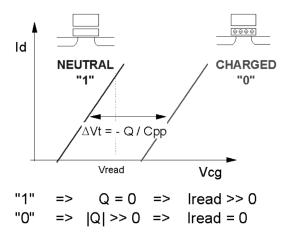

| 2.20 | NAND Flash Logic Cell                                                   |

| 2.21 | NAND: Floating-Gate MOSFET Reading Operation                            |

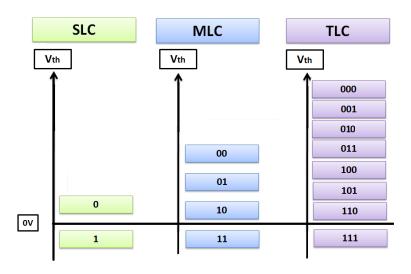

| 2.22 | SLC, MLC and TLC Memories Levels                                        |

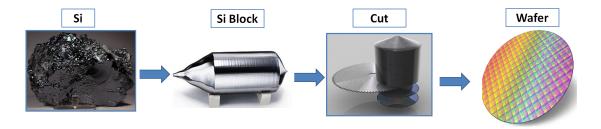

| 2.23 | From a Piece of Silicon to Wafer                                        |

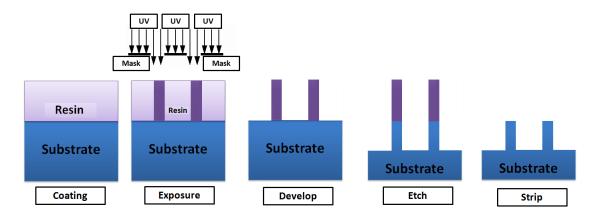

| 2.24 | Principle of Lithography                                                |

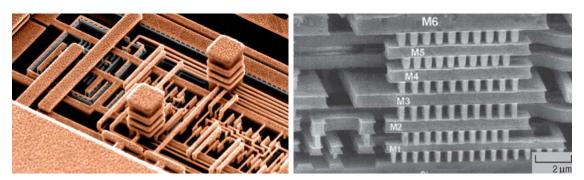

| 2.25 | Metalisation                                                            |

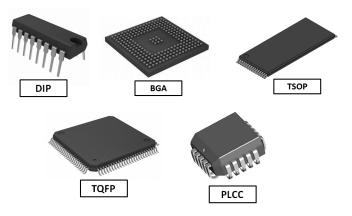

| 2.26 | Internal Chip Package                                                   |

| 2.27 | External Chip Packages                                                  |

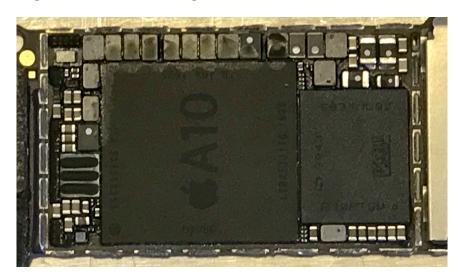

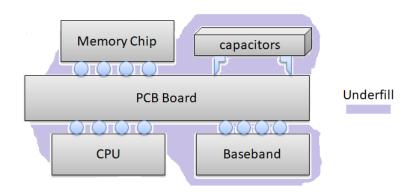

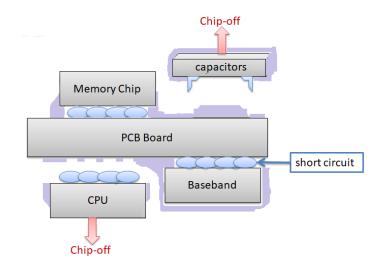

| 2.28 | Assembly of Electronic Components (A10 CPU, baseband, and capacitors)   |

|      | on the Multi-Layer PCB of the iPhone 7                                  |

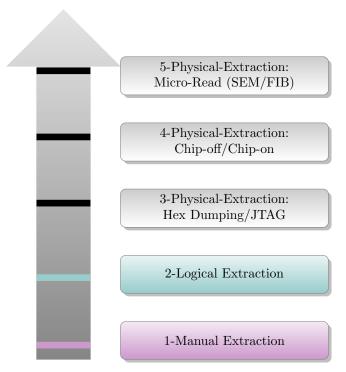

| 3.1  | Mobile Phone Extraction Levels: Ranked by Difficulty Levels             |

| 3.2  | Eclipse 3 Pro Kit                                                       |

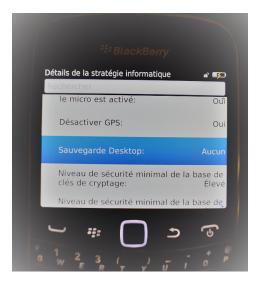

| 3.3  | BlackBerry PGP Security Policy: Backup Unauthorised                     |

| 3.4  | IRCGN's Investigators Act in CBRN Emergency Conditions 49               |

| 3.5  | Logical Extraction Communication Concept                                |

| 3.6  | Blocks of Raw Data That Can Be Carved to Find a JPEG Picture in                   |    |

|------|-----------------------------------------------------------------------------------|----|

|      | Sectors 902 to 905 [Brian, 2005]                                                  | 47 |

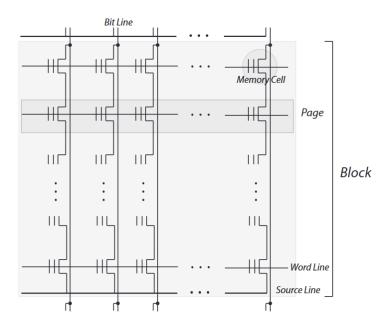

| 3.7  | Elementary Organisation of a Flash Memory                                         | 48 |

| 3.8  | Transistor Organisation of a Flash Memory                                         | 49 |

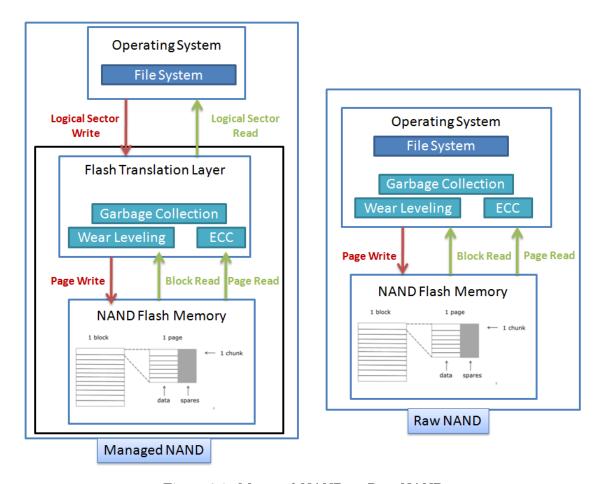

| 3.9  | Managed NAND vs Raw NAND                                                          | 52 |

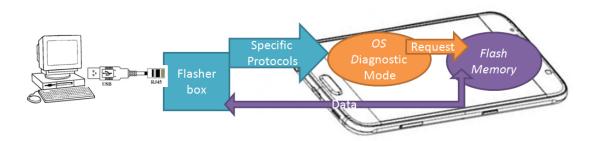

| 3.10 | Flasher Box Communication                                                         | 53 |

| 3.11 | IRCGN's Reworking Station                                                         | 56 |

| 3.12 | Memory Being Heated Before Being Unsoldered                                       | 56 |

| 3.13 | Lapping Process Steps                                                             | 58 |

| 3.14 | BlackBerry Z10: Lapping Method Unusable                                           | 59 |

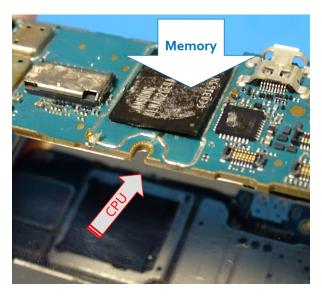

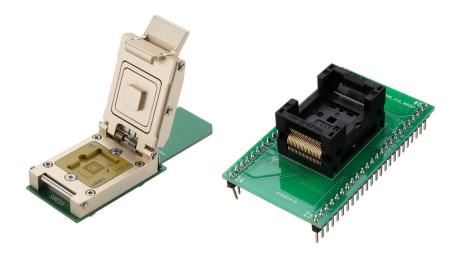

| 3.15 | eMMC and TSOP Memory Adapters                                                     | 60 |

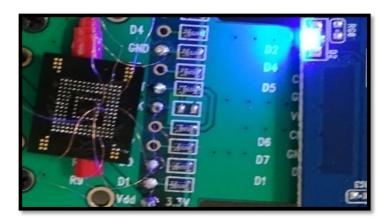

| 3.16 | Wire-to-Wire Method on eMMC Controller Via Secure Digital Protocol $$ .           | 60 |

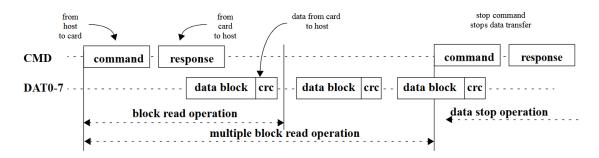

| 3.17 | eMMC 8 Bits Read Operation Using Wire to Wire Method [JEDEC, 2010]                | 61 |

| 3.18 | IRCGN's FPGA Reader: NFI Memory Toolkit II                                        | 61 |

| 3.19 | Schematic of the NFI Memory Toolkit II                                            | 62 |

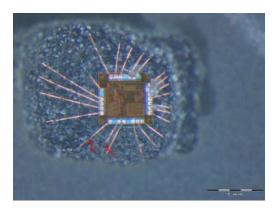

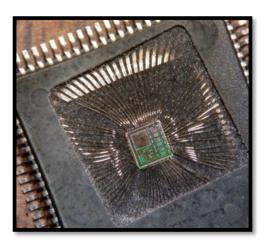

| 3.20 | Silicon Chip After Acid Attack                                                    | 62 |

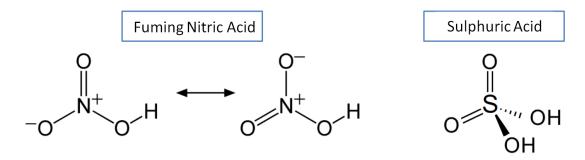

| 3.21 | Nitric Acid and Sulphuric Acid Molecular Patterns                                 | 63 |

| 3.22 | Memory Chip After Acid Attack                                                     | 64 |

| 3.23 | Silicon Memory Chip After Laser Attack                                            | 65 |

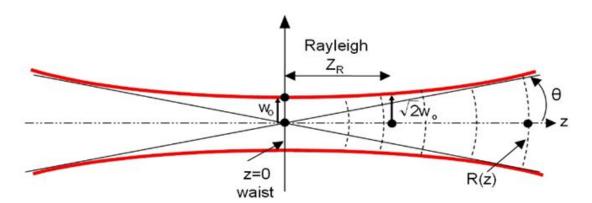

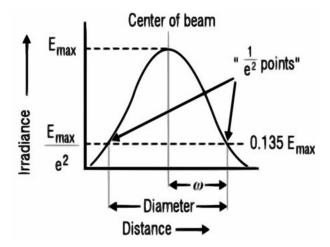

| 3.24 | The Spatial Intensity of the Beam Along the Axis z of Propagation, With           |    |

|      | $w_0$ the Minimum Radius of the Laser Beam, at the Waist                          | 66 |

| 3.25 | The Spatial Intensity of the Beam Along the Plane (x, y) Perpendicular            |    |

|      | To the Axis of Propagation                                                        | 66 |

| 3.26 | IRCGN's 1064 nm Laser                                                             | 67 |

| 3.27 | Ablation of Chip's Package by 1064 nm Laser                                       | 68 |

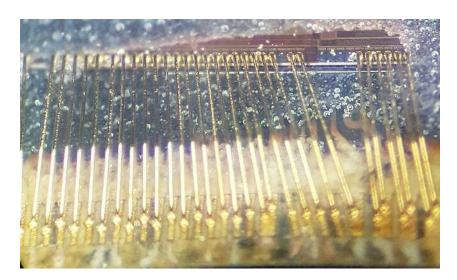

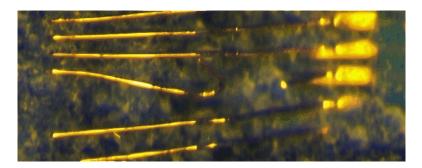

| 3.28 | Memory Chip's Bonding Wires Access After 1064 nm Laser Decapsulation              | 68 |

| 3.29 | Probing Station                                                                   | 69 |

| 3.30 | Needle Micro-Probe in Contact With Silicon Memory                                 | 69 |

| 3.31 | SD Bus Reading on eMMC's Silicon Via Probing                                      | 70 |

| 3.32 | FIB-Matter Interactions [Ay et al., 2012]                                         | 71 |

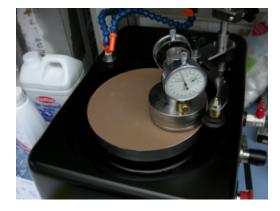

| 3.33 | Cambridge Lapping Machine [Courbon et al., 2016]                                  | 71 |

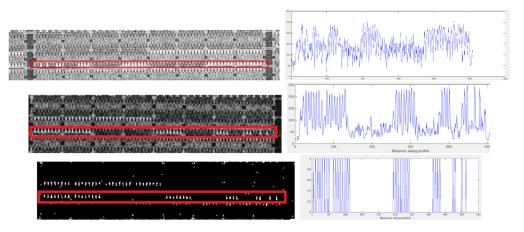

| 3.34 | Cambridge 0s and 1s Memory Extraction Using Intensity Values Variation            |    |

|      | [Courbon et al., 2016]                                                            | 72 |

| 3.35 | Damaged and Undamaged Mobile Devices Decision Diagram                             | 74 |

| 3.36 | iPhone With External Device Destruction Following a Shock                         | 74 |

| 3.37 | Mobile Device Damaged by Immersion                                                | 75 |

| 3.38 | Mobile Phone After Air Crash                                                      | 76 |

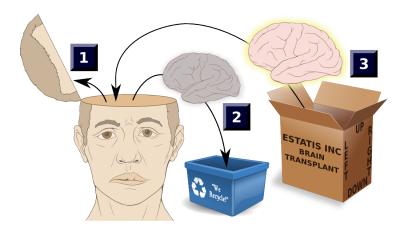

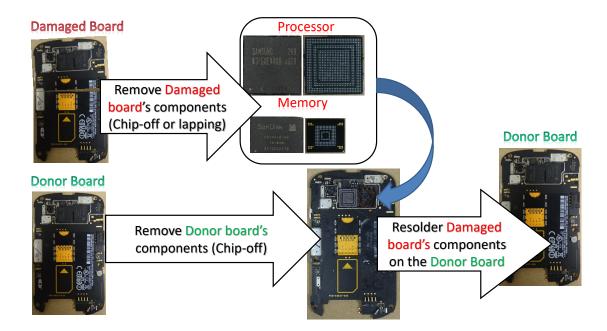

| 3.39 | A Healthy Body (Board) Used To Salvage a Rescued Brain (Chip) $\ \ldots \ \ldots$ | 77 |

| 3 40 | Transplantation Mechanism                                                         | 77 |

| 4.1  | General View                                                                         | 81  |

|------|--------------------------------------------------------------------------------------|-----|

| 4.2  | X-ray Tube                                                                           | 81  |

| 4.3  | IRCGN's X-ray Tomography Equipment                                                   | 81  |

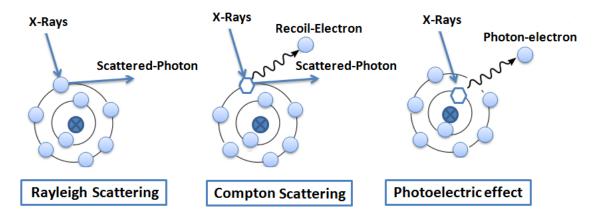

| 4.4  | X-Ray-Matter Interactions                                                            | 82  |

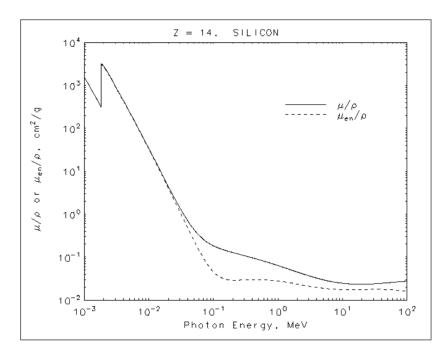

| 4.5  | X-ray–Silicon Total Linear Attenuation Coefficient (NIST)                            | 83  |

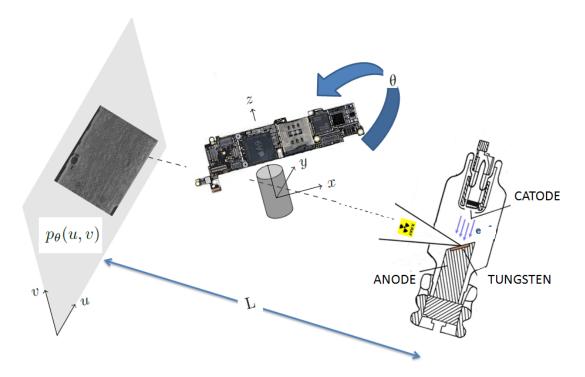

| 4.6  | X-ray Tomography Principle                                                           | 84  |

| 4.7  | Filtered Back-Projection Algorithm                                                   | 85  |

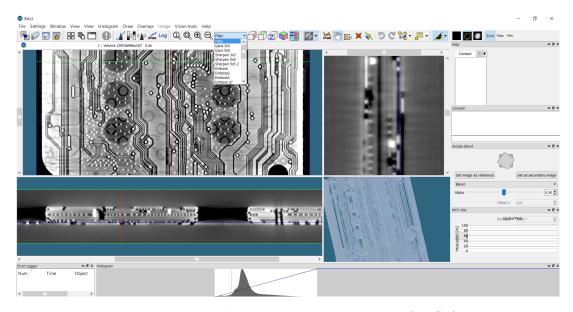

| 4.8  | Tomography Post Treatment Using X-Act Software                                       | 86  |

| 4.9  | IRCGN's SEM                                                                          | 87  |

| 4.10 | SEM Fundamental Principals                                                           | 88  |

| 4.11 | Particle–Material Interactions                                                       | 88  |

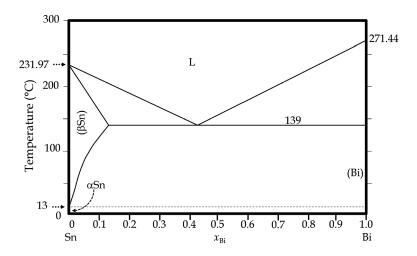

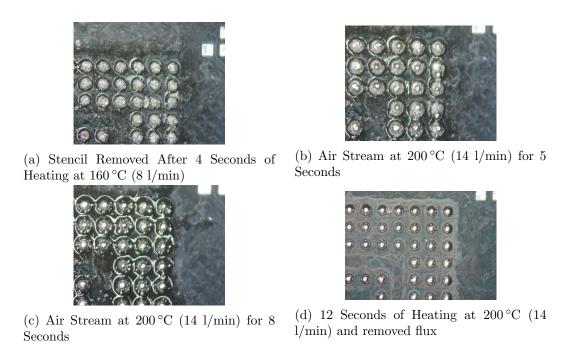

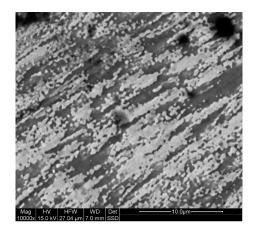

| 4.12 | 42Sn/58Bi System Phase Diagram [Aller et al., 1996]                                  | 90  |

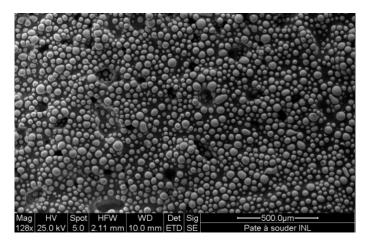

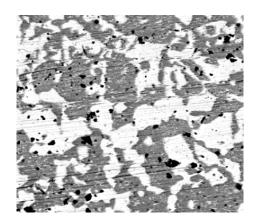

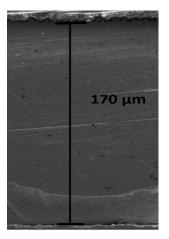

| 4.13 | 42Sn/58Bi Past Observed at 500 µm Scale (SEM)                                        | 90  |

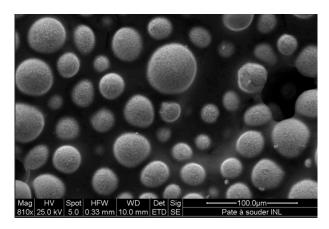

| 4.14 | 42Sn/58Bi Alloy Observed at 100 μm Scale (SEM) $\ \ldots \ \ldots \ \ldots \ \ldots$ | 91  |

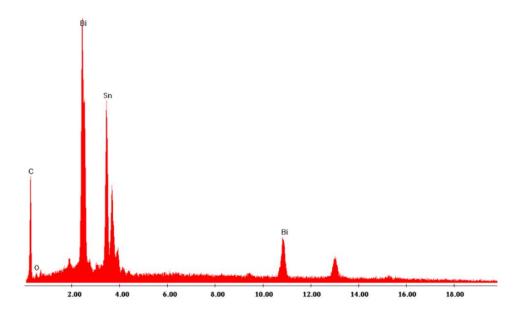

| 4.15 | 42Sn/58Bi Alloy Energy Dispersive X-ray Analysis                                     | 91  |

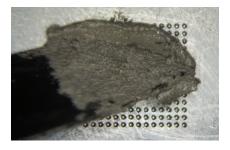

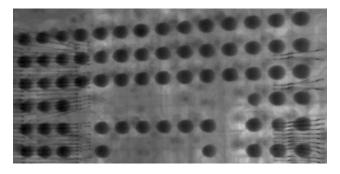

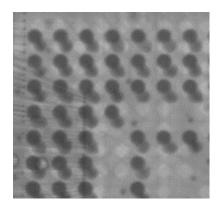

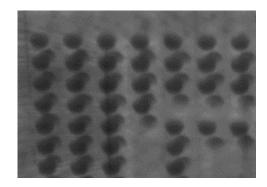

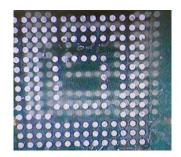

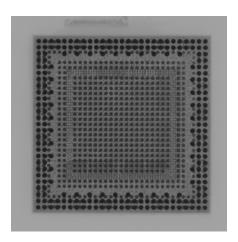

| 4.16 | Hynix H9DP4GG4JJAC Ball Grid                                                         | 92  |

| 4.17 | Step 1                                                                               | 92  |

| 4.18 | Step 2                                                                               | 93  |

| 4.19 | Step 3                                                                               | 93  |

| 4.20 | Step 4                                                                               | 93  |

| 4.21 | Step 5                                                                               | 94  |

| 4.22 | Step 6                                                                               | 94  |

| 4.23 | Balls Observed at Binocular Microscope During the Agglomeration Process              | 95  |

| 4.24 | Sn–Bi vs Sn–Pb Alloy Comparison                                                      | 95  |

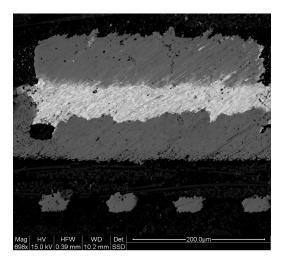

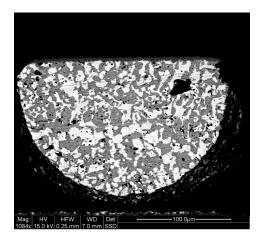

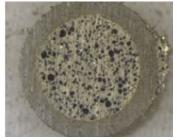

| 4.25 | (Scanning Electron Microscope (SEM)) Sn–Bi Sphere between eMMC                       |     |

|      | (left) and PCB (right), Slow Cooling                                                 | 96  |

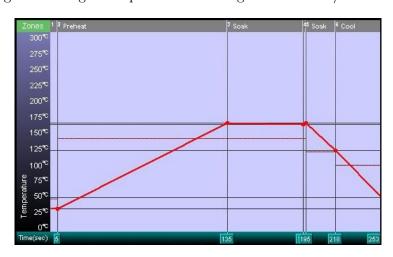

|      | Fast Cooling (1.9 °C/s) Reflow Profile, X-axis (seconds), Y-axis (Celsius) .         | 96  |

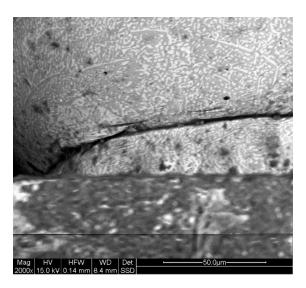

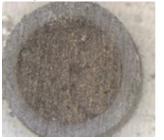

| 4.27 | Polished Section of Soldering Using Standard Metallography Techniques $$ .           | 97  |

| 4.28 | Slow Cooling (0.13 °C/s) Reflow Profile, X-axis (seconds), Y-axis (Celsius)          | 97  |

| 4.29 | At Fast Cooling Rate                                                                 | 98  |

| 4.30 | At Slow Cooling Rate                                                                 | 98  |

| 4.31 | Microstructure of 42Sn/58Bi Solidified Balls                                         | 98  |

| 4.32 | Bismuth and Tin Agglomerated Into Coarse Structures                                  | 98  |

| 4.33 | Crack Within the Ball Caused by Slow Solidification                                  | 99  |

| 4.34 | Fast Solidification                                                                  | 99  |

| 4.35 | Slow Solidification                                                                  | 99  |

|      | Distance Between PCB and Chip                                                        | 99  |

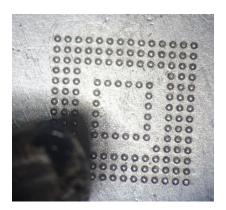

|      | 9                                                                                    | 100 |

|      |                                                                                      | 101 |

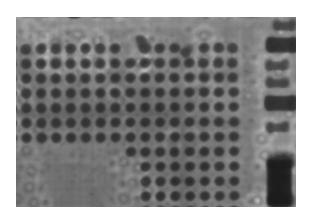

| 4 39 | Soldering Performed Correctly: X-ray View Using 90° Incidence                        | 101 |

| 4.40 | Well-Prepared Soldering Confirmed by Tilt Radiography (45° Incidence) . 10         |

|------|------------------------------------------------------------------------------------|

| 4.41 | Incidence $90^{\circ}$                                                             |

| 4.42 | Incidence $45^{\circ}$                                                             |

| 4.43 | X-ray Views of Incorrectly Performed Soldering: Chip/PCB Misaligned . 10:          |

| 4.44 | Migration of a Micro-Ball to the eighbouring beads: X-ray Visualisation . 102      |

| 5.1  | TCA Used for BGA Soldering With Board [Zhang et al., 2013] 108                     |

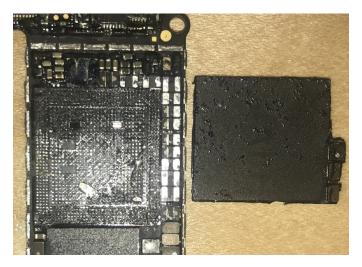

| 5.2  | Good De-Soldering                                                                  |

| 5.3  | Bad De-Soldering Due to Underfill                                                  |

| 5.4  | Printed Circuit Boards After De-Soldering                                          |

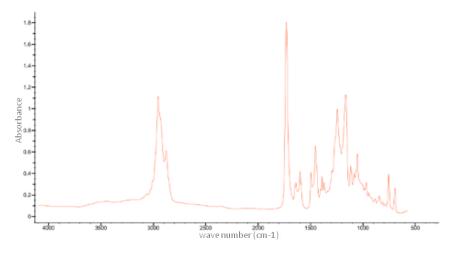

| 5.5  | Thermal Adhesive Absorbance (Polytec)                                              |

| 5.6  | i<br>Phone 7's Underfill Between Memory and PCB $\ \ldots \ \ldots \ \ldots \ 100$ |

| 5.7  | Thermomechanical Deformation Without and With Underfill $\dots \dots \dots 10^{r}$ |

| 5.8  | Underfill Modelling                                                                |

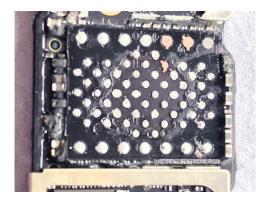

| 5.9  | i<br>Phone 7 Memory and Neighbourhood Capacitors Glued on Board $\ \ldots \ 108$   |

| 5.10 | Destruction of the Neighbourhood Capacitors Due to Underfill on iPhone             |

|      | 7 CPU After Classical Chip-Off                                                     |

| 5.11 | Destruction of the Neighbourhood Capacitors After Classical Chip-Off . 110         |

| 5.12 | UV-Adhesive Absorbance (Polytec)                                                   |

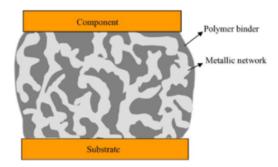

| 5.13 | Ball Created by an Assembly of a Polymeric Binder Matrix and Metal                 |

|      | Filler [Li and Wong, 2006]                                                         |

| 5.14 | Damaged Micro-USB Connector Repair                                                 |

| 5.15 | Pads Restored                                                                      |

| 5.16 | Nordson Performus II Pump                                                          |

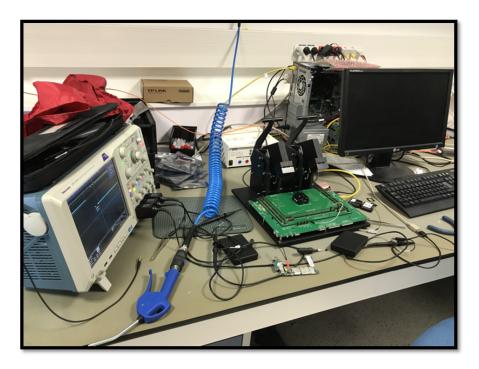

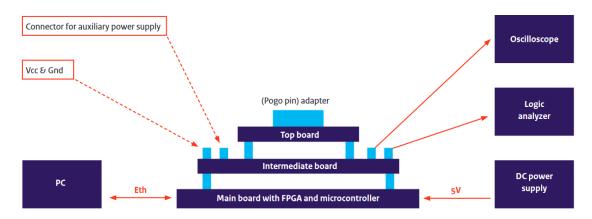

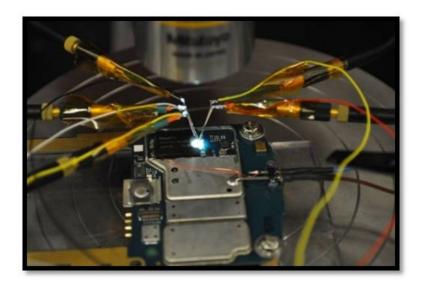

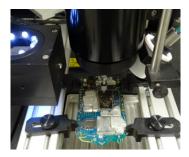

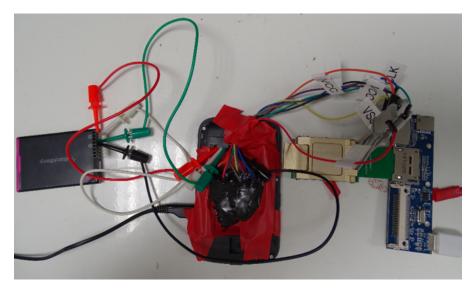

| 5.17 | Thesis' Memory Man-In-the-Middle Prototype Being Prepared 114                      |

| 5.18 | Adhesives in Reworking and Prototyping                                             |

| 5.19 | eMMC Controller Scheme [JEDEC, 2010]                                               |

| 5.20 | IRCGN's X-ray 3D Micro-Tomography of the H9DP4GG4JJMCGR Hynix                      |

|      | eMMC                                                                               |

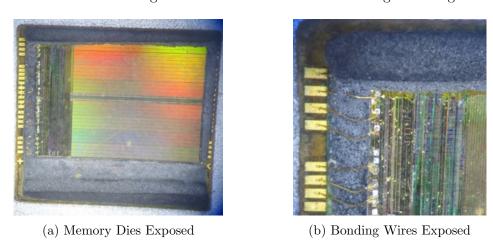

| 5.21 | eMMC Decapsulated                                                                  |

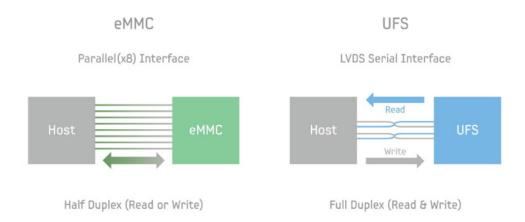

| 5.22 | eMMC Universal Flash Storage (UFS) Interface Comparison [Samsung, $2015$ ]11       |

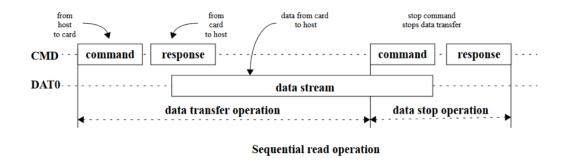

| 5.23 | Sequential Read Operation: 1 Bit Data Bus                                          |

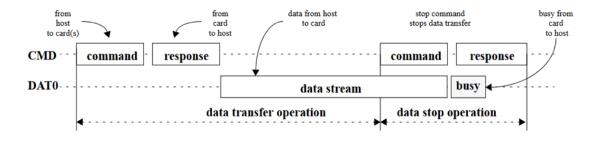

| 5.24 | Sequential Write Operation: 1 Bit Data Bus                                         |

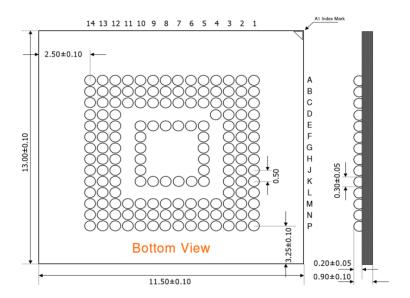

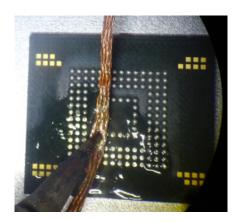

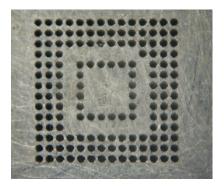

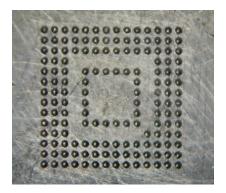

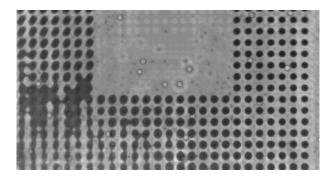

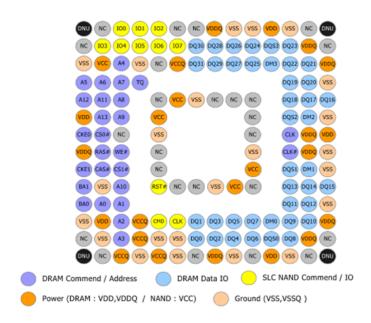

| 5.25 | Mapping Schematic Balls of the H9DP4GG4JJMCGR Hynix eMMC 118                       |

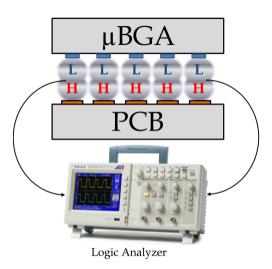

| 5.26 | Our MIM Attack Using Two Levels of BGA: (L) Low-temperature, (H)                   |

|      | High-temperature                                                                   |

| 5.28 | Step 3: Depositing ECA                                                             |

| 5.30 | Step 6: Fixing Wires With Thermally Conductive Adhesive (TCA) and                  |

|      | UV Adhesive (UVA)                                                                  |

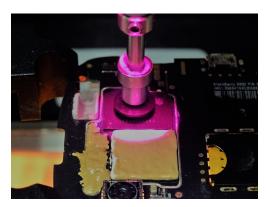

| 5.31 | Step 7: Low Temperature Re-Balling Technique                                       |

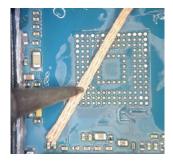

| 5.32 | Step 8: Using the Soldering Ball Grid Array (BGA) Station                                        | 122 |

|------|--------------------------------------------------------------------------------------------------|-----|

| 5.33 | Step 9: X-ray to Check the Position                                                              | 122 |

| 5.34 | Step 10: General View of the Prototype                                                           | 122 |

| 5.35 | Reading Phase Process: BlackBerry 9790 PGP                                                       | 123 |

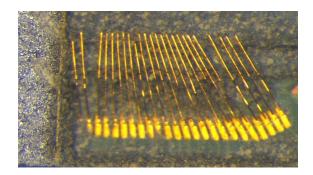

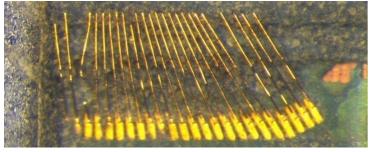

| 5.36 | Reinjection Phase in the eMMC: BlackBerry 9790 PGP                                               | 124 |

| 5.37 | Tracking Signals Using a Logic Analyser or an FPGA                                               | 125 |

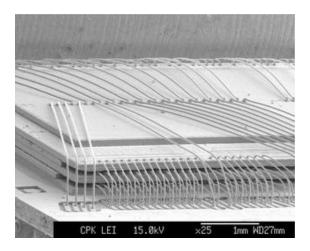

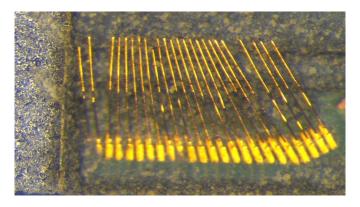

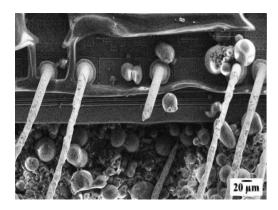

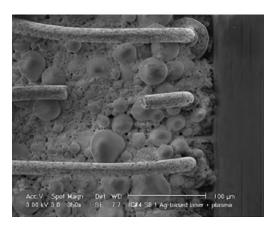

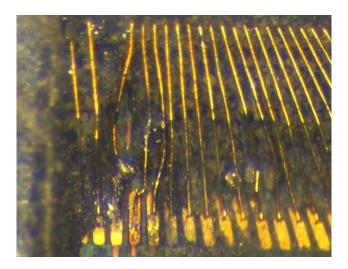

| 6.1  | SEM Images of Broken Copper Wires After Complete Decapsulation (Laser                            |     |

|      | and Chemical) [Kor et al., 2014]                                                                 | 128 |

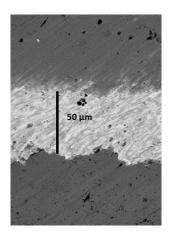

| 6.2  | SEM Image of Attacked and Broken Wire [Kerisit et al., 2014a]                                    | 128 |

| 6.3  | Image of Broken Wire After Probe Manipulation $\ \ldots \ \ldots \ \ldots \ \ldots$              | 128 |

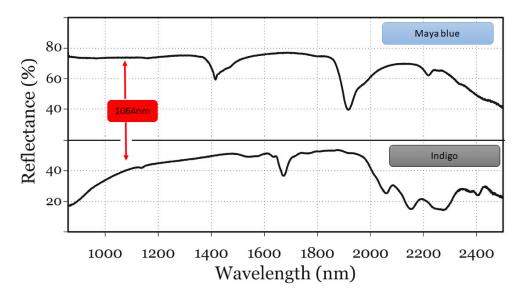

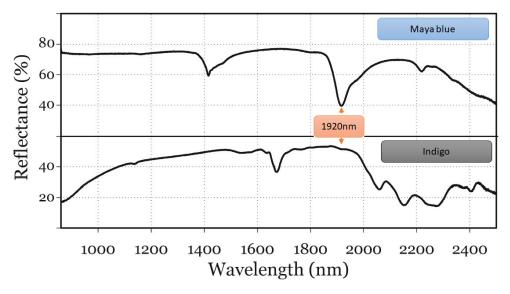

| 6.4  | Indigotin (C $_{16}{\rm H}_{10}{\rm N}_2{\rm O}_2)$ and Maya Blue Reflectance Spectra, 1064nm $$ | 132 |

| 6.5  | Indigotin $(\mathrm{C_{16}H_{10}N_2O_2})$ and Maya Blue Reflectance Spectra, 1920 nm $$          | 132 |

| 6.6  | Experimental Protocol                                                                            | 133 |

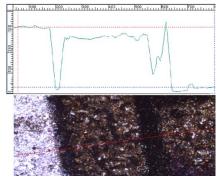

| 6.7  | Laser Interaction on ECA Without Dye or Pigment                                                  | 134 |

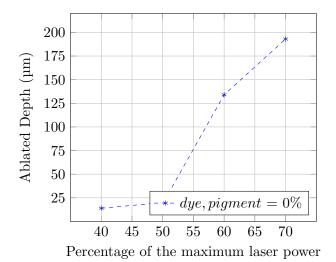

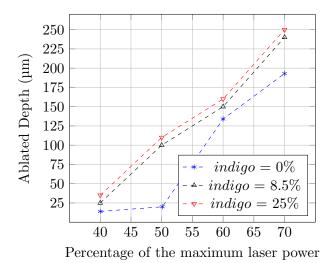

| 6.8  | Without Dye and Pigment: Measurement of the Average Ablated Depth                                |     |

|      | (Averaged Over 5 Measurements) Using the Focal Plane Microscope $\ . \ . \ .$                    | 134 |

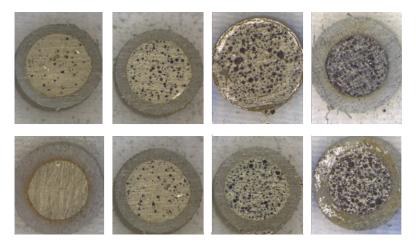

| 6.9  | (Left to Right), Bottom: $0\%$ , $1.5\%$ , $3\%$ , $7\%$ , Top: $4.5\%$ , $8.5\%$ , $17\%$ and   |     |

|      | 25% of Indigotin Dye                                                                             | 135 |

| 6.10 | Indigo: Measurement of the Average Ablated Depth (Averaged Over 2                                |     |

|      | Measurements) Using the Focal Plane Microscope                                                   | 135 |

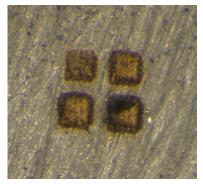

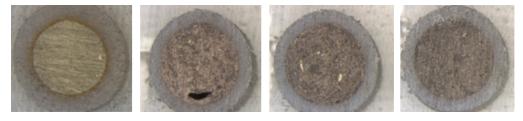

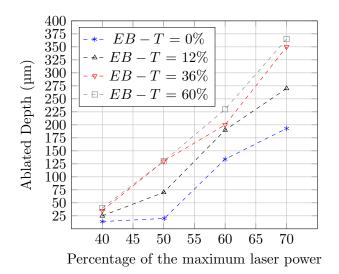

| 6.11 | (Left to Right) 0%, 12%, 36%, and 60% of Eriochrome Black T $\ldots$ .                           | 136 |

| 6.12 | Eriochrome Black T: Measurement of the Average Ablated Depth (Aver-                              |     |

|      | aged Over 2 Measurements) Using the Focal Plane Microscope                                       | 137 |

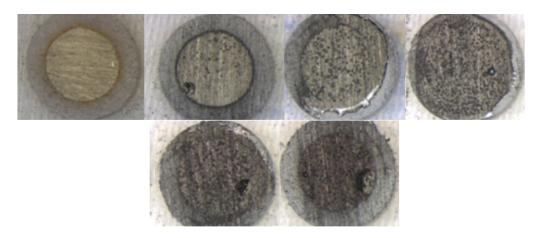

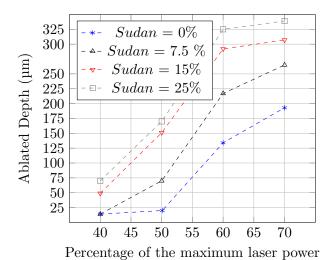

| 6.13 | (Left to Right, Top: 0%, 1.5%, 7.5%,15%, Bottom: 25%, and 35% of                                 |     |

|      | Sudan Black Pigment                                                                              | 137 |

| 6.14 | (Left to Right, Top to Bottom) Sudan Black: Measurement of the Average                           |     |

|      | Ablated Depth (Averaged Over 2 Measurements) Using the Focal Plane                               |     |

|      | Microscope                                                                                       | 138 |

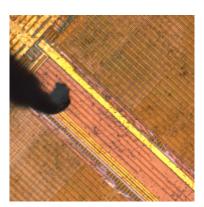

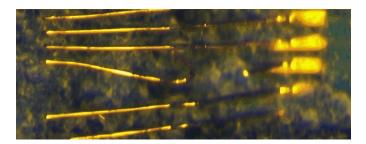

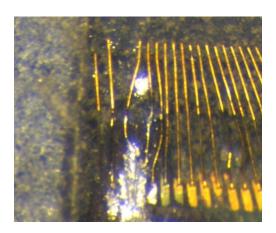

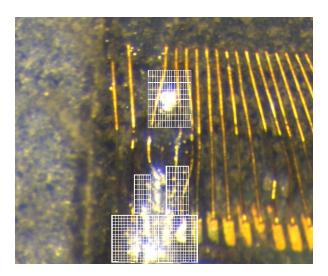

| 6.15 | Bonding Wire Access After 1064 nm Laser Decapsulation                                            | 139 |

| 6.16 | Micro-Probe Bonding Destruction                                                                  | 139 |

| 6.17 | Application of the Pigmented ECA                                                                 | 139 |

| 6.18 | Mask Superpositioned to Define the Laser Beam Path                                               | 140 |

| 6.19 | Repair Result After 4 Passes of the Laser at 40% of the Maximum Power                            | 140 |

| 6.20 | Eriochrome (Left), Indigo (Right)                                                                | 141 |

| 6.21 | Eriochrome (Left), Indigo (Right): Cavity After Laser $\ \ldots \ \ldots \ \ldots$               | 142 |

| 7.1  | Package On Package Component Principle                                                           | 143 |

| 7.2  | BlackBerry and Samsung Stacked CPUs                                                              | 144 |

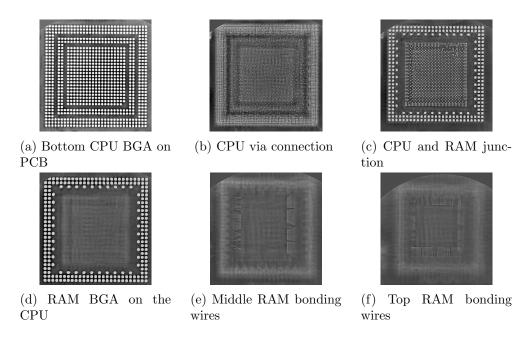

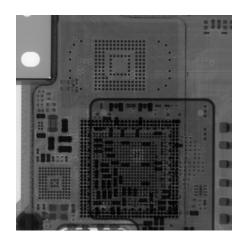

| 7.3  | BlackBerry 9900 PoP CPU X-ray Images                                                             | 144 |

| 7.4  | Chip-Off PoP CPU Destruction and Hooke's law                                                     | 145 |

#### List of Figures

| 7.5  | Resin (Left), Hardener (Right)                                                           |

|------|------------------------------------------------------------------------------------------|

| 7.6  | eMMC Memory Broken Bonding Wire                                                          |

| 7.7  | Application of the HTTTCA                                                                |

| 7.8  | Chip-Off: Classical Process                                                              |

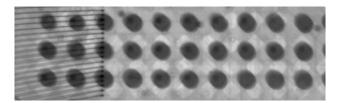

| 7.9  | X-ray Control to Ascertain That the PoP Component Has Not Moved $$ 149                   |

| 7.10 | Donor Board eMMC Gap Position                                                            |

| 7.11 | Soldering Confirmation on the Donor Board                                                |

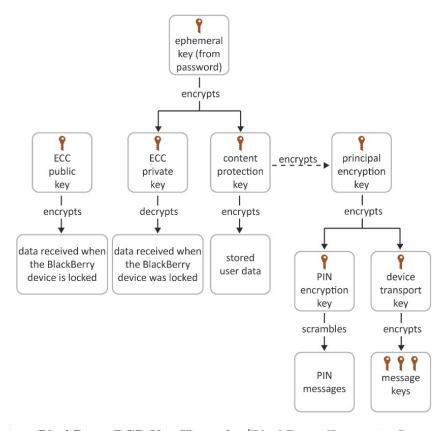

| 7.12 | Simplified BlackBerry Encryption Process                                                 |

| 7.13 | BlackBerry 9900 PoP CPU and Memory X-ray Soldering Control 152 $$                        |

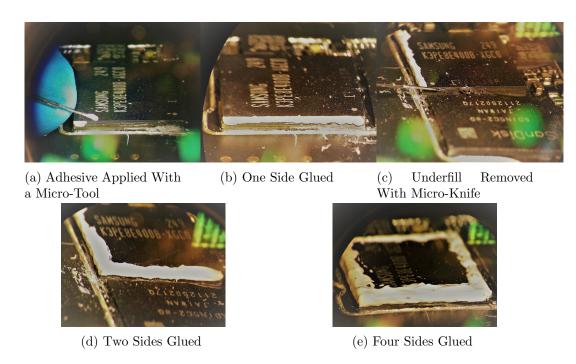

| 7.14 | Step 3: Adhesive Deposited Between the Stack of the PoP CPU 153                          |

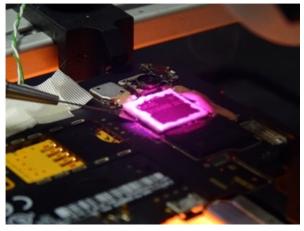

| 7.15 | BlackBerry 9900 Po<br>P ${\mbox{CPU}}$ Unsoldering Using Chip-Off/TCA Technique<br>. 153 |

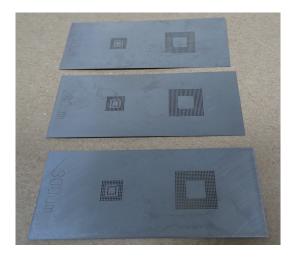

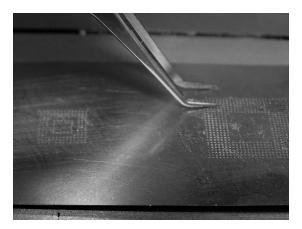

| 7.16 | Reballing Process Using Stencil                                                          |

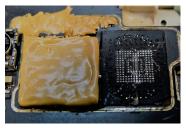

| 7.17 | Step 7: Donor Board Preparation                                                          |

| 7.18 | Checking eMMC Positioning and Good Soldering on X-ray $\ \ldots \ \ldots \ 156$          |

| 7.19 | Turn on Transplanted BlackBerry 9900 PGP                                                 |

# List of Tables

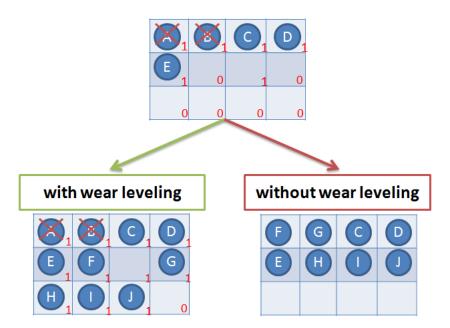

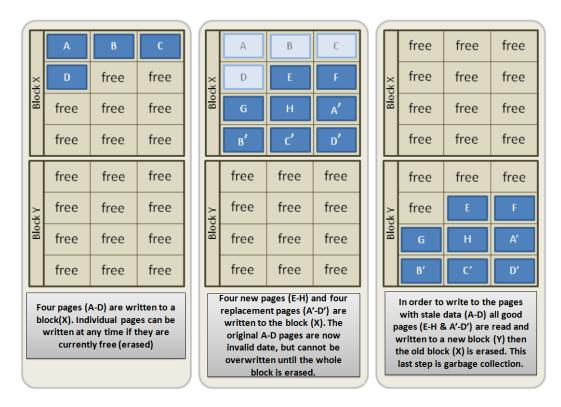

| 3.1 | Wear Leveling in Flash Memories                                       |

|-----|-----------------------------------------------------------------------|

| 3.2 | Garbage Collector in Flash Memories                                   |

| 3.3 | 16-State Machine: JTAG IEEE [Maunder, 1993]                           |

| 6.1 | Synthesis of the Two Types of Colouring Matter                        |

| 7.1 | BlackBerry PGP Key Hierarchy [BlackBerry-Entreprise-Server, 2014] 151 |

| В.1 | File Signatures: Headers and Footers                                  |

| B.2 | File Starts: File Identifications                                     |

# 1

# Introduction

Nowadays, many civilians are living with a continuous threat of terrorism or mass accident, such as the Nice attack [BBC-News, 2016], the Paris attack [BBC-News, 2015b], the Germanwings crash [BBC-News, 2017], and the Puisseguin accident [BBC-News, 2015a]. Forensic investigators must frequently bypass the protection mechanisms of embedded systems to extract data, which constitutes evidence for the criminal court. Terrorism or mass accident, as we see, are current topics in our society, and the bypassing of security mechanisms must also be made possible so both legal questions (proof in court, understanding the disaster) and ethical challenges (mourning of the victims' families) can be answered.

During our research, we have worked on the interface of theoretical physics and computer security, and have brought some new physics approaches to forensic investigations. The main objective of this thesis has been the implementation of innovative methods of extraction, and the physical bypass of cryptographic mechanisms to assist investigators and experts in their investigations.

On December 2nd 2015, a terrorist attack was carried out on behalf of the Islamic State in San Bernardino, California, United States. Two heavily armed terrorists burst into a centre for unemployed people, and began shooting, causing 14 deaths and 22 wounded [Time, 2015]. The US authorities finally managed to kill the two suspects. As part of a judicial investigation operation conducted by the US authorities, an Apple iPhone 5C mobile phone, running iOS 9, belonging to one of the terrorists was found. The encrypted phone was unfortunately protected by an unknown lock code with a mechanism of physical erasure of the data after 10 attempts. Knowing that a four-digit passcode has 10,000 possibilities, in February 2016, the US Federal Bureau of Investigation (FBI) announced that it was unable to unlock the phone. Apple declared not to have the passcode, and the FBI asked Apple to code up a new version of iOS 9 without the 10-guess limit. The FBI actually wanted to brute-force the passcode, but Apple refused to do that. Therefore, FBI filed a complaint against Apple to force them to create a tool allowing the unlocking of the phone. However, the case did not go to court, because the FBI managed to find a solution, with the help of a third party, to unlock the phone. The

security point of phones (like Apple, BlackBerry or Samsung) is a selling point. What can be a stronger advertising message than saying that Apple itself and the police are unable to access the user's data?

This first example shows the authorities' new interest in collaborating with external laboratories or universities. Before the San Bernardino attack, for confidentiality reasons, investigators were often closed to communicating on their means and their advances. But the high level of cryptography and the rapid evolution of technology has forced investigators to open up to new collaborations, without which the judicial investigations would end up without a quick solution. It is in this context that this thesis took place, with a strong collaboration between the Forensic Sciences Institute of the French Gendarmerie (IRCGN) and the academic world: École Normale Supérieure (ENS) of Paris; the Smart Card and IoT Security Centre (part of the Information Security Group) of Royal Holloway, University of London; the School of Biological Sciences of Royal Holloway; and the University of Cambridge Computer Science Department.

At a press conference [Keizer, 2016], on March 24th 2016, the FBI Director, James Commey, told reporters that the technique call "NAND mirroring" would never work. However, just after this announcement, Dr Sergei Skorobogatov, from the Computer Science Department of the University of Cambridge, proved the opposite and showed it in his paper: "The bumpy road towards iPhone 5c NAND mirroring" [Skorobogatov, 2016]. It is from this moment that forensic investigators were convinced that universities could be allies in the search for judicial evidence.

In this context, in which manufacturers do not want to exchange information with state authorities, forensic investigators must resort to new methods. However, before going into the technical details of this thesis, the current context firstly leads us to question three points:

- What does the French law say about the use of cryptography (section 1.1.1)?

- What are the legal penalties for crimes commission using cryptography (section 1.1.2)?

- What is the investigator's legitimacy to carry out the reverse engineering of encrypted systems (cryptanalysis) before extracting and analysing the data (section 1.1.3)?

It is in this sense that we will present in section 1.1 the laws that protect forensic investigators. Indeed, without these laws, investigators could be prosecuted for hacking activity within the meaning of  $Article\ 323-1$  of the  $French\ Criminal\ Code^1$ .

<sup>&</sup>lt;sup>1</sup>Article 323-1 of the French Criminal Code, Legislative Section, Book 3, Title 2, Chapter 3.

A question beyond the scope of this thesis is the possible evolution of the French legal framework to force manufacturers to reveal a back-door or create software in the context of terrorist activities and criminal offences. For the time being, parliamentarians and lawyers see it as an infringement of individual freedom. They also see it as an unworkable legislation because it would aim to ban some mobile phone brands in French territory. This question was, and is still, valid when writing this thesis, and at the time of the production of the facial recognition decipher system (face ID) of the Apple iPhone X. Thus, in September 2017, a French deputy<sup>2</sup> proposed an amendment which prohibited the commercial sale and distribution in France of the iPhone X, in case of a terrorism threat. The question is far from being decided, and the investigators have to face the new technologies and must be inventive.

## 1.1 Forensic Investigators in the Face of Cryptography: French Law

Cryptography (protocols, symmetric or asymmetric ciphers) has been widely democratised in recent years, but it is regulated both for individuals and for experts mandated to extract data protected by cryptographic algorithms. The regulation on cryptography aims at preserving the internal or external security of the state. There is a constant tension between the defence of the state's interests (confidentiality) and the preservation of individual rights (individual privacy).

In addition, France must also face a context where European Union legislation aims to harmonise the legislation of its Member States. The legal framework for forensic experts is a pillar that the justice system seems to want to strengthen. However, the expansion of cryptographic technologies is faster than the legislative framework [Freyssinet, 2012].

#### 1.1.1 The Birth of Cryptography in French Law

French law defined cryptology for the first time in Act no. 90-1170 of December 29th 1990, on the regulation of telecommunications<sup>3</sup>. The law provides that cryptological services are all services intended to transform information, or signals, into unintelligible information for third parties. The law also mentions the reverse operation, using means, hardware or software designed for this purpose.

Cryptography can be used in different sectors and may create safety problems, particularly at the commercial or state security level. Data security becomes a marketing

$<sup>^2</sup> http://www.lci.fr/politique/eric-ciotti-veut-encore-faire-interdire-les-produits-apple-en-france-2064289.html$

<sup>&</sup>lt;sup>3</sup>Official Journal of the French Republic n. 303, December 30th 1990, Page 16439, Paragraph 28.

argument for encrypted phones (Apple iPhone, BlackBerry PGP), encrypted messaging applications (Telegram messenger, WhatsApp messenger) and on-line purchase (Apple pay, Android pay). Criminals can divert the ethical and lawful use of cryptography to prepare, disseminate and communicate offences. In the area of forensics, we frequently find the illegal uses of cryptography in international narcotics trafficking, the preparation and commissioning of terrorist attacks, in industrial spying and assassination files. The possibilities of using cryptography for criminal purposes are numerous, and the list keeps on growing.

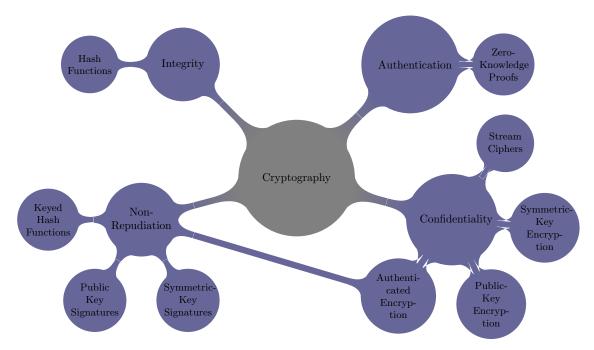

Cryptography is subsequently clearly defined in Section 29 of the Act of June 21st 2004<sup>4</sup>, and in that sense, cryptological means any hardware or software designed or modified to transform data. It can be either information or signals that use secret conventions, or to perform the inverse operation with secret conventions. The main purpose of these cryptographic means (Figure 1.1) is to guarantee the security of the storage or the transmission of data, making it possible to ensure its confidentiality (information accessible only to authorised persons), its authentication (to be sure of author identity) or the control of its integrity (no message alteration).

Figure 1.1: The Broad Fields of Cryptography [Menezes et al., 1997]

Cryptography within the legal framework aims at ensuring examination and authentication functions. In this sense, French laws have introduced some protocols for entering and for outputting cryptographic devices on national territory.

<sup>&</sup>lt;sup>4</sup>Act n. 2004-575, June 21st 2004 for Confidence in the Digital Economy, LCEN.

If the software imported from a Member State of the European Union does not perform only control and authentication functions, an authorisation from the French Prime Minister will also be needed so the cryptographical means can be understood: source code, software and hardware. The software imported from other States will also need prior authorisation from the French Prime Minister. These applications are then sent to the French National Cybersecurity Agency<sup>5</sup> (ANSSI).

Decree No. 2007-663 of May 2nd 2007<sup>6</sup> and the Order of January 29th 2015<sup>7</sup> define the form and the content of the declaration files relating to the means of cryptology. It should be noted that some categories of cryptological means remain free to import or export. These categories concern, for example, the supply of equipment intended for the general public, such as radio or television reception, mobile phones, and on which most of the cryptographic capacity is not accessible to the user.

Through these French laws encrypted phones can freely and legally circulate on national territory. Both the forensic investigators and the users do not have access to the encryption mechanism operation. It will be seen in section 1.1.3 how French law allows forensic investigators to carry out the reverse engineering of encrypted systems (cryptanalysis) to access the phone's content.

#### 1.1.2 The Criminal Sanctions Against the Illegal Use of Cryptography

When cryptology is used for illegal purposes, the law provides for a general mechanism for increasing sentences. Thus, *Article 132-79 of the French Criminal Code*<sup>8</sup> provides for the systematic increase of the penalty when criminals are using cryptology.

When a means of cryptology, within the meaning of Article 29 of Act no. 2004-575 of June 21st 2004, has been used for the preparation or commission of a crime or offence, the maximum penalty of deprivation of liberty shall increase as follows:

- It is liable to imprisonment for life when the offence is punishable by thirty years' imprisonment.

- It shall be increased to thirty years' imprisonment when the offence is punishable by twenty years' imprisonment.

- It shall be increased to twenty years' imprisonment when the offence is punishable by fifteen years' imprisonment.

- It shall be increased to fifteen years' imprisonment when the offence is punishable by ten years' imprisonment.

<sup>&</sup>lt;sup>5</sup>http://www.ssi.gouv.fr/en/

<sup>&</sup>lt;sup>6</sup>Decree n. 2007-663 adopted for the application of Articles 30, 31 and 36 of the LCEN.

<sup>&</sup>lt;sup>7</sup>Order of January 29th 2015: https://www.legifrance.gouv.fr

<sup>&</sup>lt;sup>8</sup>Legislative Section, Book 1, Title 3, Chapter 2, Section 3, Article 132-79.

- It is increased to ten years of imprisonment when the offence is punished by seven years of imprisonment.

- It shall be increased to seven years' imprisonment when the offense is punishable by five years' imprisonment.

- It shall be doubled when the offense Is punishable by a maximum of three years' imprisonment.

However, the provisions of this article do not apply to the perpetrator or accomplice of the offence if he has given a clear version of the encrypted messages and secret agreements necessary for decryption, as requested by the judicial authorities. This mechanism of aggravation is means of negotiation for investigators to increase the pressure on criminals. Unfortunately, if the investigator has no other means of proving the crime than the encrypted data, the article cannot be validated before the French courts. If no evidence is brought in before the courts, then there are no means of criminal punishment.

Article 434-15-2 of the Criminal Code<sup>9</sup> punishes anyone who has knowledge of the secret deciphering convention of a cryptology device, which may have been used to prepare, facilitate or commit a crime or offence, and refuses to hand over this convention to the judicial authorities, despite the authorities' requisitions. Such an act is punishable, by French Criminal Code, by three years of imprisonment and a fine of 45,000 euros.

In addition, as an amendment has been dropped by Article 16 of the Act No. 2016-731 of June  $3rd\ 2016^{10}$  which increases even more the level of penalties.

The law, therefore, provides for sanctions against perpetrators, accomplices of a crime, and against any other persons who are aware of an agreement of data deciphering used to commit or attempt to commit a crime.

#### 1.1.3 Extracting Encrypted Data: the Experts' Work Legitimacy

The French Code of Criminal Procedure provides for two scenarios, depending on the nature of the infringement:

- The first one is when the infringement is a minor offence (consumption of narcotic drugs, theft, fraud, etc.).

- The second one is when the infringement is a criminal offence (terrorism, drug trafficking, assassination, child pornography, etc.).

The appointment of a judge, called "the opening of a judicial investigation", is decided by the public prosecutor. A judge is mandatory when the facts are criminal. Thus, at

<sup>&</sup>lt;sup>9</sup>Criminal Code, Legislative Section, Book 1, Title 3, Chapter 1, Section 9, Article 434-15-2.

<sup>&</sup>lt;sup>10</sup>Act n. 2016-731 of June 3rd 2016 "strengthening the fight against organized crime, terrorism and their financing and improving the efficiency and guarantees of criminal proceedings".

the opening of a judicial investigation, the judge is responsible for the investigations. Before the opening, the public prosecutor is responsible for the investigations. The Code of Criminal Procedure says that when it appears that data, seized or obtained during the investigation, has been encrypted, the authorities in charge of the case (public prosecutor or judge) may appoint an expert for a criminal offence or a qualified person for a minor offence to decipher the information: Article 230-1 of the Code of Criminal Procedure, amended by Article 15 of the Act no. 2014-1353 of November 13th 2014.

The law favours investigators when the data is protected by an authentication mechanism that prevents the access and understanding of the encrypted information contained in it. Thus, when the data entered was obtained during the investigation and has been transformed, the public prosecutor or the investigating judge may order the expert to carry out the technical operations of reverse engineering to be able to obtain access to the information. The objective is to obtain a clear version of the data, and in the case where means of cryptography has been used, to obtain the secret decryption agreement.

If the sentence incurred is equal to, or greater than, two years' imprisonment and if the investigations require specific cryptanalysis operations, the public prosecutor (or the judge) may prescribe recourse to the State's means subject to the secrecy of national defence<sup>11</sup>. The magistrate, who has control of the case, has the power to help the expert by allowing him to use military means to decipher the data (calculators). The aim is to give investigating magistrates the means to access the clear content of encrypted messages. Thus, judges may use the services of experts in cryptanalysis, as well as the means of the State covered by the secrecy of national defence.

Reverse engineering is therefore legal if the expert (or qualified person) follows the rules set by the Code of Criminal Procedure, Article 230-1: encrypted data for criminal offences (or minor offences) and a public prosecutor or judge's authorisation. The work of the expert is, therefore, authorised and regulated by French law.

#### 1.2 Thesis Outline

With the increasing evolution of technologies and the generalisation of the use of cryptography, forensic investigators need to resort to new methods of data extraction (cryptanalysis). This forensic thesis deals with several topics related to bypassing the protection mechanisms and cryptographic implementations of embedded systems to help forensic investigators to extract and analyse data. The main contributions of this thesis are:

$<sup>^{11}\</sup>mathrm{Code}$  of Criminal Procedure, Legislative Section, Book 1, Title 4, Chapter 1, Article 230-1.

- A new low-temperature soldering method minimising silicon thermal shock on electronic chips. The method reduces the risk of data modification/destruction during forensic desoldering operations.

- A new modus operandi of advanced repair of damaged electronic components after air crash, fire, submersion or terrorist attack by using various physico-chemical properties of adhesives.

- Development of a new method called "Chip Adhesives Method (CAM)" which is a Ball-Grid-Array Man-In-the-Middle (BGA-MIM) platform. The CAM allows investigators to provide advanced access to all exchanges in real time between CPU, memory and crypto-components. Thus, they can understand and modify the implemented security mechanisms inside secure mobile devices.

- Development of a new modus operandi that makes polymeric adhesives sensitive to laser decapsulation attacks while decreasing the laser power deposited during ablation.

- A new laser bond repair method with an accuracy of 15 micrometres.

- A new electrically conductive adhesive chemical composition using pigmentation properties.

- A new procedure called "PoP chip-off/TCA Technique" which allows forensic investigators to unsolder Package On Package (PoP) components without either damaging or destroying them.

- The full forensic transplantation of the BlackBerry PGP (Pretty Good Privacy).

**Organisation.** Chapter 2 introduces integrated circuit and logic design, from a transistor to hardware cryptochip. General semiconductors theory and fundamental operations are detailed in the first section. The second section shows the different types of memories on silicon chips and the constitution of their fundamental logic cells. The last section presents the manufacturing process of silicon memories from a piece of silicon to packaging memories.

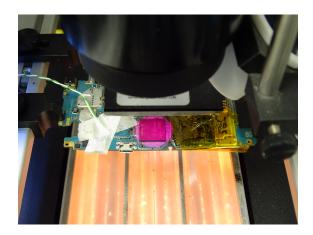

Chapter 3 introduces the techniques used by forensic investigators to recover data on smartphones. The first section describes techniques used for undamaged mobile devices (manual extraction and logical extraction). The second section is devoted to the physical extraction and forensic hardware reverse engineering techniques applied to flash memory devices: chip-off, chip-on, attack by fuming nitric acid, ablation with laser cutter and nano-probing. The third section presents in detail techniques used for damaged and unsecured mobile devices. The last section shows an advanced technique developed during this thesis, called "forensic transplantation", used for damaged and secured mobile devices.

Chapter 4 details the fundamental study of the 42Sn/58Bi alloy and its forensic applications to the low-temperature re-balling and re-soldering of BGA components. The first section presents the limits of traditional unsoldering techniques. The second section consists of a theoretical study which presents the 42Sn/58Bi alloy fundamental properties and introduces two reverse engineering techniques: X-ray tomography and Scanning Electron Microscope. The last section is the practical part showing some PhD investigations' experimental results applied to 42Sn/58Bi alloy.

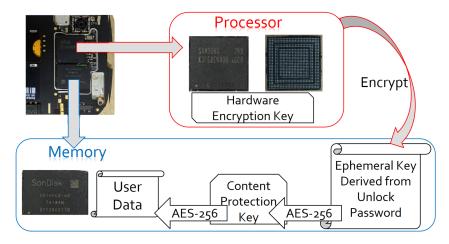

Chapter 5 describes polymer adhesive methods used in this thesis for advanced forensic applications. The first section presents the limits of traditional forensic methods through concrete cases. The second section introduces the material used and fundamental properties. The third section is devoted to developing new methods for solving the first section's limits. In the last section, we use the fundamental properties of adhesives to develop a memory man-in-the-middle platform. The platform is used for tracking signals between memory and CPU and to understand or modify the implemented security mechanisms inside secure mobile devices.

Chapter 6 presents a fundamental use of the laser cutter in the micrometric repair of an electronic component. Through concrete cases, the first section presents the limits of traditional forensic methods. The second section consists of a theoretical study of pigments and dyes. The third section presents some experimental results and the two industrial patents filed. The last section presents a direct forensic application case: the repair of a broken micrometric bonding wire.

Chapter 7 presents a method developed to transplant Package on Package (PoP) components and fundamental forensic reverse engineering methods. The first section presents traditional techniques and limits used by forensic experts. The second section describes the method developed to unsolder PoP components without destruction. The third section introduces, for the first time, the process developed during this thesis for the full transplantation of a damaged secured mobile phone using a hardware key on the processor of a BlackBerry 9900 PGP.

Chapter 8 concludes this thesis and sets out future work and advancements.

#### 1.3 Publications

This thesis is primarily based on the publications described in this section. Among the developed work are 5 published papers, 2 patents and several talks in France, Canada, Belgium and the United Kingdom.

# Low-Temperature Low-Cost 58 Bismuth—42 Tin Alloy Forensic Chip Re-Balling and Re-Soldering

with David Naccache, Thomas Souvignet and Sebastien Lepeer

**Abstract.** The re-soldering of electronic components is often necessary during forensic investigations. Such re-soldering usually occurs in two scenarios. In the first *in vivo* scenario, a component is extracted from the exhibit board and analysed (or unlocked) externally before being re-implanted in the exhibit board. In the second *in vitro* scenario, the extracted component is implanted in an external test board or an unlocked device of the same brand and model. We call such manipulations chip-off/chip-on procedures.

In some cases, data manipulation, performed during chip-off and chip-on, may also help to recover forensically significant data such as emails, text messages, contacts, photos or videos. Chip-off/chip-on techniques involve two risky steps during which forensic data can be irreversibly lost, given that a chip must be de-soldered and re-soldered again. During both operations, temperatures beyond the normal operating range are applied to a chip containing valuable information. In addition, for cost reasons, chips are usually not designed to withstand repeated soldering during their life-cycle.

A recent publication by the Netherlands Forensic Institute [Jongh, 2014] proposes to minimise thermal stress by using low-temperature alloys during the re-soldering phase. The necessary low soldering temperature 42Sn/58Bi 300 µm balls has a burdensome cost (several thousands of euros per ball jar) if a mass production is not considered. Given that the forensic analysis of mobile telephones has become a standard requirement in most criminal cases, unitary forensic analysis cost reduction is currently a necessity. Luckily, it is possible to find cheap soldering pastes composed of inhomogeneous balls of 42Sn/58Bi (25—45 µm) mixed in a solvent. How to use such pastes for forensic re-soldering proves to be a nontrivial laboratory exercise, on which we focus in this paper.

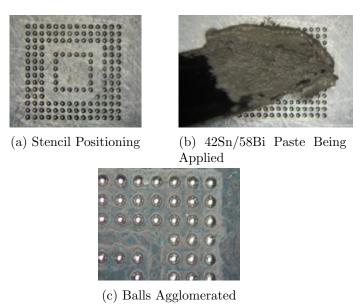

This work introduces a method called reballing, that will produce 300-micron beads from 25- to 45-micron balls. The proposed process is based on the use of a reballing stencil. We analyse the influence of the temperature descent curve during soldering and explore its effects on the final soldering quality. Finally, we will verify the compliance of our low-cost (less than 40 euros), low temperature (138°C), curve-optimised reworking process on micro-BGA components.

**Note.** This work is presented in detail in Chapter 4.

Electrically Conductive Adhesives, Thermally Conductive Adhesives and UV Adhesives in Data Extraction Forensics

with David Naccache and Thomas Souvignet